本文始于2024年01月,以2021R2 SPISim(SPISim是一家专门做IBIS、IBIS-AMI模型生成的软件公司,于2020年被ansys收购)演示从IO DSPF Netlist(Detailed Standard Parasitic Format)生成IBIS模型的全过程,文章中不仅包含了IO结构的相关基础知识和详细的操作流程,还有一些软件使用过程遇到的一些问题及相关的注意事项。

注意:本文列举的IO类型为输入输出类型的IO,其他类型IO也可参考本文。

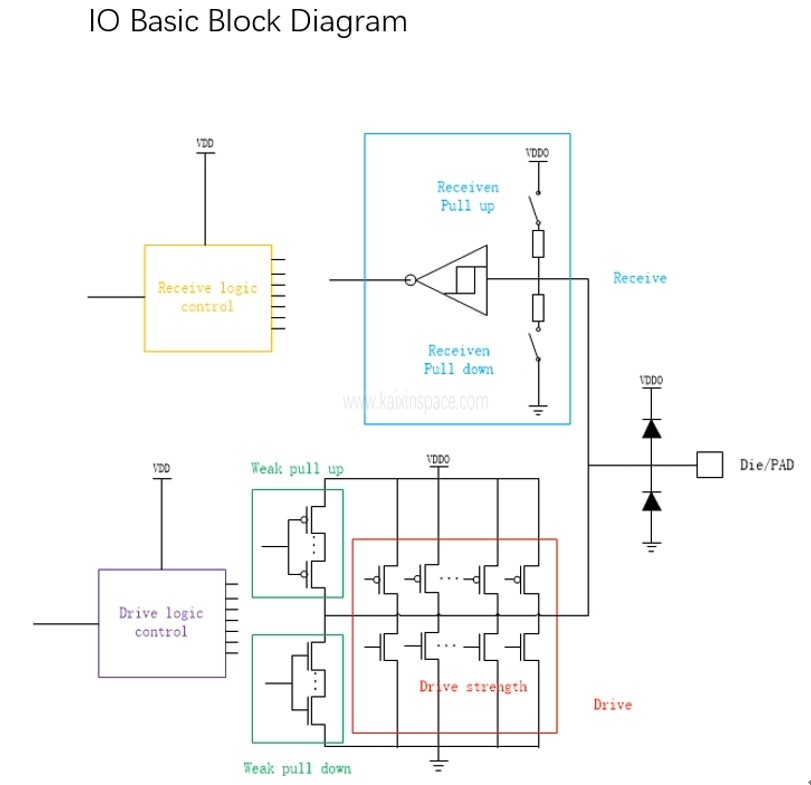

1. IO基本结构示意图

如下图片是双向IO的基本结构示意图:

2. IO相关特性说明

需要了解并掌握IO中和生成IBIS模型相关的引脚节点。如下:

① 电源和地节点

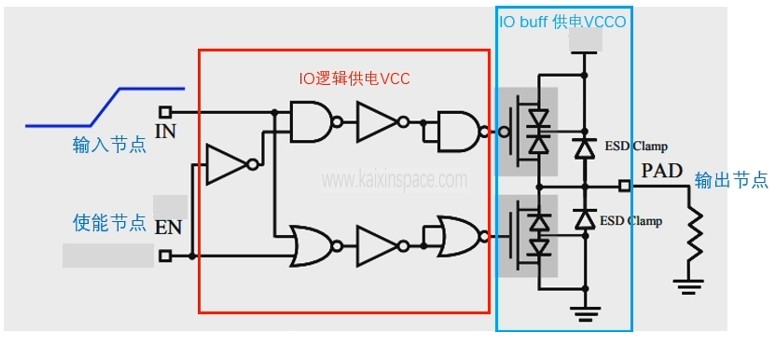

注意这里电源会区分,是给IO逻辑电路供电VCC和IO buff供电VCCO,两者电源电压会不一样;如下图所示;

② 输入(In)、输出(Die/Output)、使能(En)节点,如果此IO buff类型是diff,还需要找出对应diff输入和输出节点。

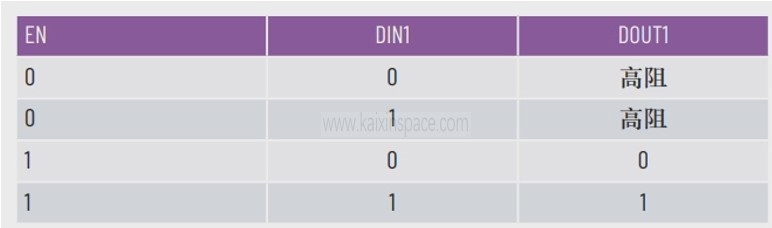

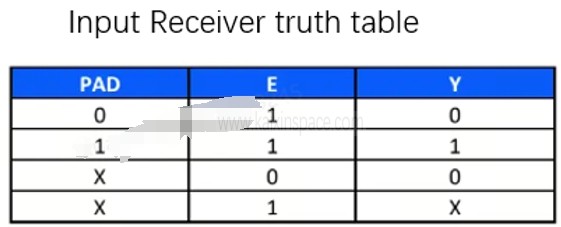

注意:这里需要着重说明下使能(En)节点;这里En节点是指能控制输出节点在高阻和非高阻(输出是0或1)之间切换的引脚,如下图;

从上图可以明显看出,当EN为0时,输出是高阻,当EN是1时,输出是非高阻。

提醒:在不同的IO的电路中,控制输出节点在高阻和非高阻(输出是0或1)之间切换的引脚可能不止一个,有可能是好几个共同决定,此时应理清IO中使能引脚的关系。这对后续是否能正确生成IBIS模型至关重要,请务必仔细再仔细!!!

③ 影响输出相关特性的管脚,如:控制驱动能力的引脚、控制边沿特性的引脚、弱上拉和弱下拉引脚等。

这里额外说一点,除了上述IO相关的信息需要了解外,还需准备如下相关资料:

- IO版图对应工艺节点的器件模型(SPICE/HSPICE);

正常情况下,厂商会给出对应IO的 DSPF netlist网表,网表中会包含IO原理图中的连接关系以及物理连接之间的寄生参数。但提供的网表中一般不含有基本器件子电路定义和对应的模型(包含device model 的corner(tt、ss、ff) 参数),这也是体现IBIS中不同corner的重要参数来源。举例如下:

注意:不同corner的参数需要在spisim工具里单独设置。此点在后续实例演示中会有相关操作。

基本器件包含:nmos、pmos、resistance、capacitor….

- 对应IO的 DSPF netlist 文件

不多说,显然这是生成IBIS的主角。

3. 实例演示

3.1 相关资料准备

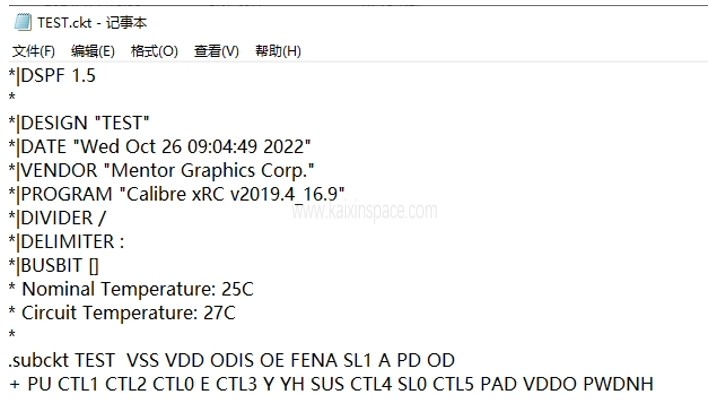

3.1.1 DSPF netlist 原始文件和对应IO的datasheet;

- DSPF网表文件部分截图如下

至于“DSPF网表格式的解释”请读者直接百度查找即可。

- Datasheet文件

3.1.2 IO网表对应的device or transistors HSPICE model库文件;

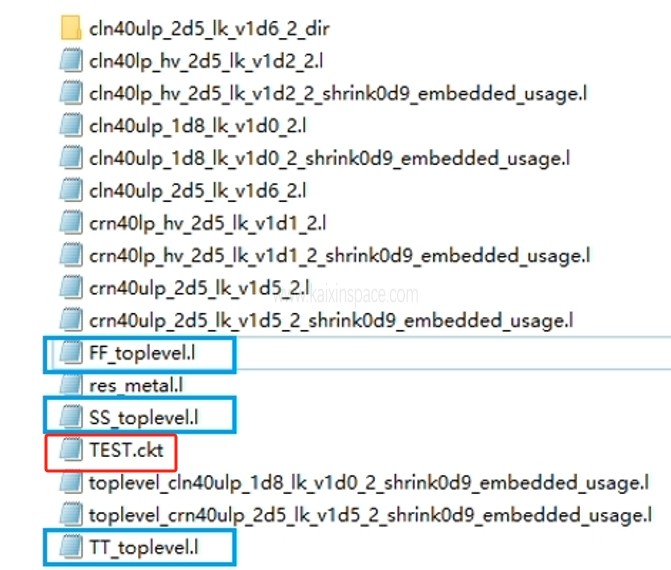

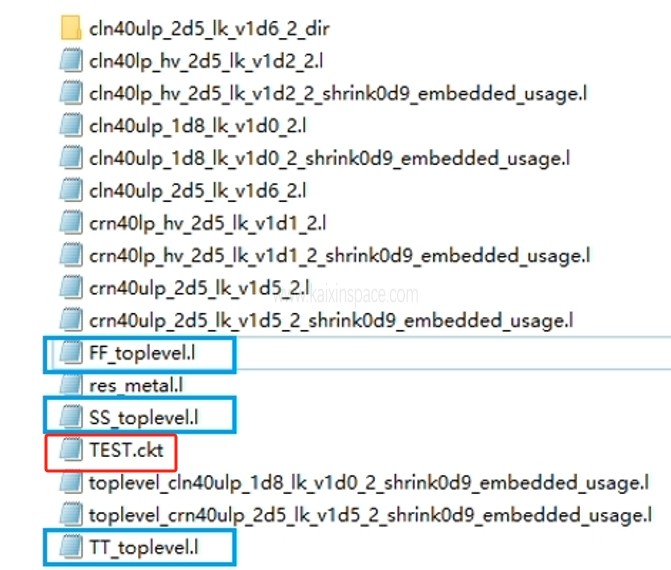

这里需要注意,需要将toplevel.l中的文件稍作修改,并增加对应不同corner(SS、TT、FF)的toplevel.l文件,方便后续在SPISim软件中调用,生成对应的corner的数据。(min、type、max)。请务必将这些文件都放到同一目录下。

修改后的toplevel.文件如下:

3.2 IO相关信息说明(和IBIS模型生成相关)

从对应的datasheet中,得到对应生成IBIS模型所需的引脚信息。

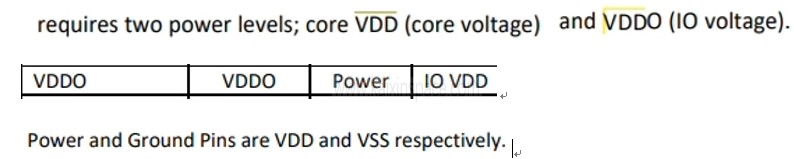

3.2.1 电源和地相关节点

从datasheet中可以得到IO的逻辑部分Power是VDD,对应buff部分Power是VDDO,对应Ground是VSS,如下图所示。

说明:由于IO中逻辑电路和buff电路有不同的供电电压域,并且它们支持不同的电压模式,在此例中我们将使用VDD=1.1V(Type)和VDDO=1.8V(Type)电压域,

3.2.2 输入、输出、使能相关节点(buff作为输出作用时的节点)

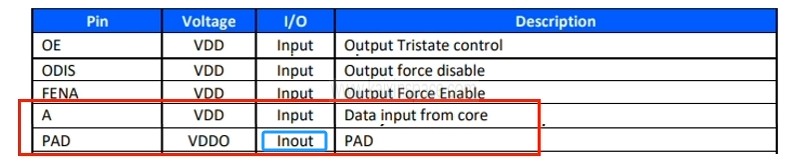

从对应的datasheet中,可以很容易得到输入节点为A,输出节点为PAD

提示注意:从下图“PAD”栏可以看到此IO的buff类型是输入输出类型。

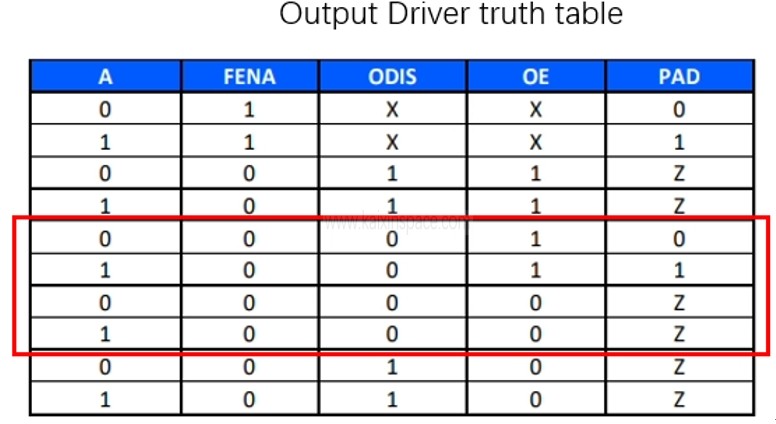

这里需要特别说明下使能节点,从上图可以看出“OE”描述是控制高阻的引脚,但仔细看“ODIS”和“FENA”引脚描述也与之输出有关。此时我们可以结合输出的真值表来确定各个引脚的电平。

上面我们讲了使能的节点是指能控制输出节点在高阻和非高阻(输出是0或1)之间切换的引脚。从下图真值表中,红框部分,可以很容易看出当,ODIS和FENA引脚都为0时,OE引脚此时控制PAD输出在高阻和非高阻之间切换。OE为1时,PAD输出为非高阻,OE为0时,PAD输出为高阻。

3.2.3 确定与输出驱动能力和边沿特性有关的节点引脚

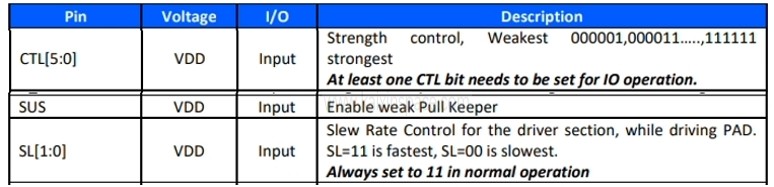

从对应的datasheet中可以看到CTL[5:0]对驱动能力有关、SL[1:0]对mos边沿特性有关;

这里要特别说明下SUS引脚,此引脚功能是在当输入A为浮空时,对输出PAD固定在一个确定电平,防止输出PAD浮动。默认此引脚电平为0,即输入A有确定输入信号。但在制作IBIS模型中建议将当输入A浮空时的情况考虑进去,以增加模型的适用范围。

提示:也有其他IO类型使用weak Pull down 和 weak Pull up来替换SUS这里的功能。

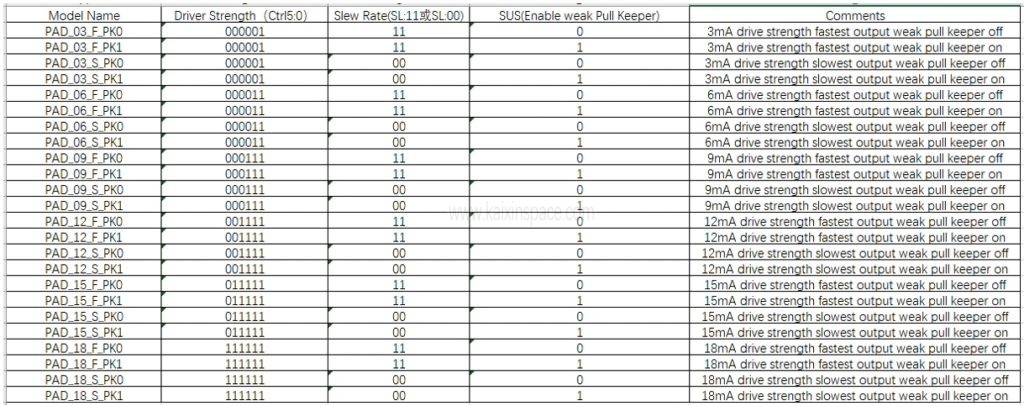

在IBIS模型中,不同驱动能力的子模型需要分开生成。故此IO对应的子模型分类整理如下:

综合3.1、3.2所述,我们确定了此IO所要生成IBIS模型的全部信息。下面将以其中一个子模型为例,通过SPISim软件来生成对应的IBIS模型。

3.3 使用SPISim生成IO对应的IBIS模型

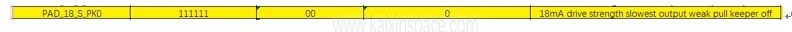

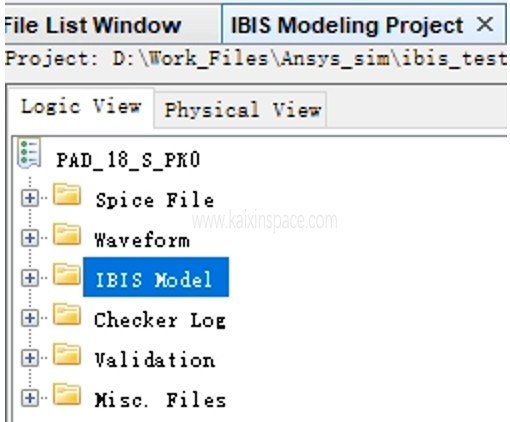

这里以子模型:PAD_18_S_PK0 为例。

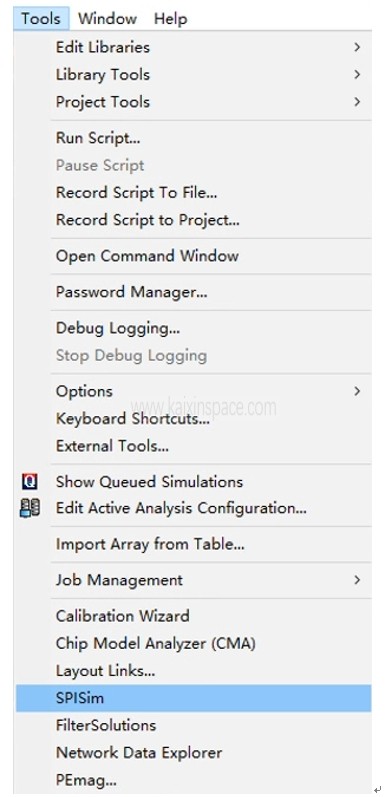

3.3.1 按照如下两种方式中的一种,启动SPISim软件。

方法1:启动Ansys EDT电子桌面,工具栏找到Tool-SPISim。

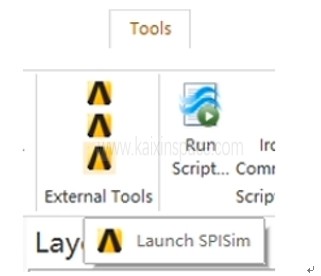

方法二:打开Ansys Siwave 软件,菜单栏Tool,点击Launch—SPISim。

弹出如下对应框:

菜单栏点击Module,选择Mpro,弹出对应对话框。

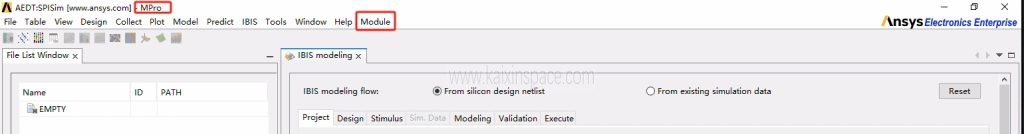

按如下图设置,其中:

- 3 为需要工作的目录;

- 4 是AEDT内默认的Nexxim模拟器,也可以根据需要选择其他模拟器(如Hspice);

- 5 是默认的IBIS语法检查器。

正常情况下,4、5 保持默认即可。

这里的 3 需要特别说明下,需要将DSPF网表和device model 库文件均放在同一目录下。

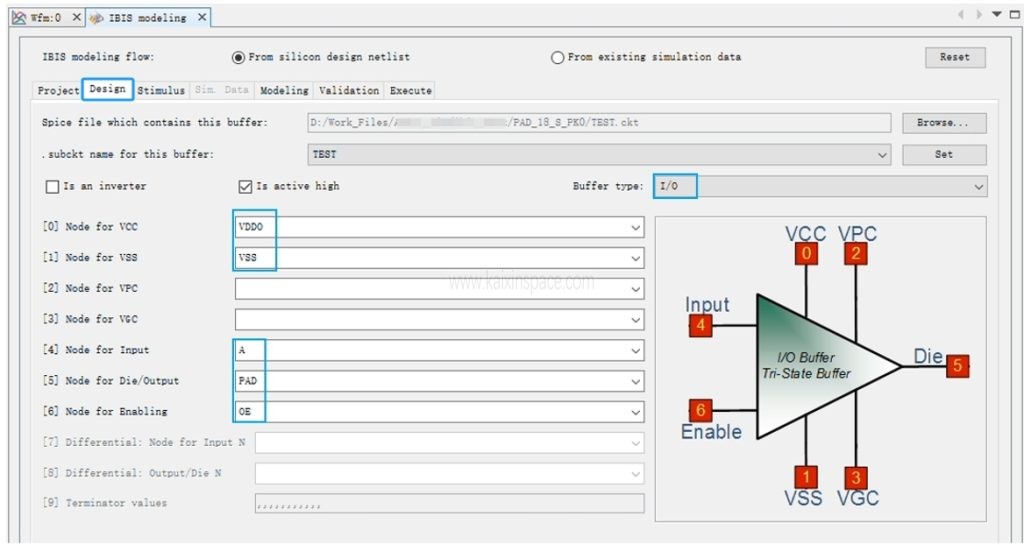

3.3.2 在Design选项中选定对应DSPF网表文件所在路径并正确设置对应的IO pin引脚名。最终设置完成如下图所示:

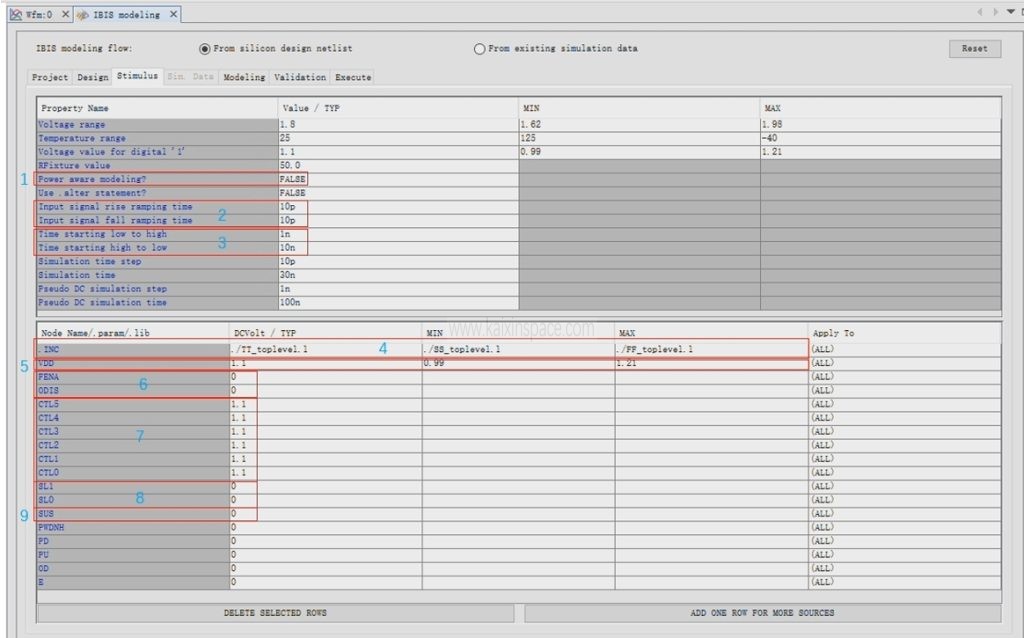

3.3.3 在Stimulus选项中设置对应仿真的各个参数。如下图所示。

这里对参数作下说明:

- 1 中的参数默认时FALSE,如果选择TRUE那么生成的IBIS模型自动变成5.1版本;

- 2 中的参数表示给定激励的上升和下降沿时间参数,这里可以给小点,一般要远小于实际被测器件本身的上升和下降时间,这样才能体现出真实的上升和下降参数;

- 3 中的参数需要注意,此参数应尽量给的稍微大点,因为mos的一些参数需要在达到平稳时的参数才是准的;

- 4 设定不同corner所对应的库模型文件;

- 5 IO逻辑部分供电电压;

- 6 配合使能OE管脚,定义高阻和非高组状态,用于不同条件下数据提取;

- 7 buff mos驱动能力配置;

- 8 buff mos 边沿特性配置;

- 9 弱保持配置;

这里需要特别说明下增加变量的功能,如下图;

这里可以增加IO中一些其他控制引脚相关的电平,如此案例中我们使用了FENA和ODIS 两个引脚共同控制使能,另外还有增加库、变量等功能,大家可以自行尝试。

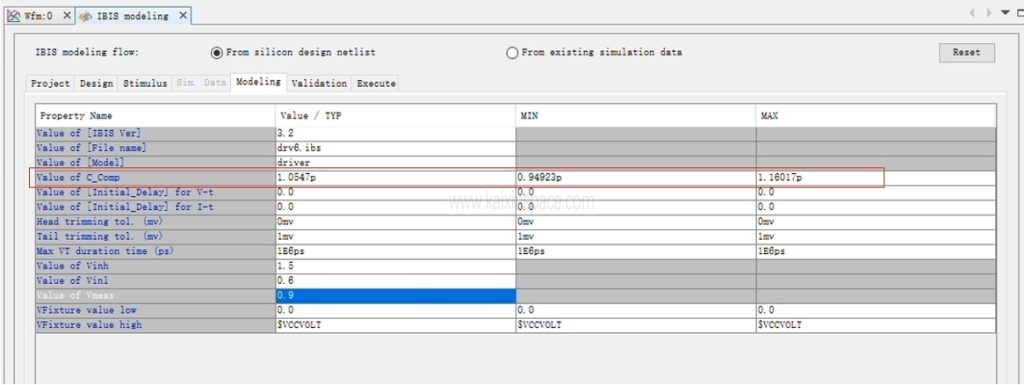

3.3.4 在Modeling选项中设置相关模型参数;如下图;

这里需要说明下C_Comp 硅片电容,一般情况下在IO后防的网表中可以得到;

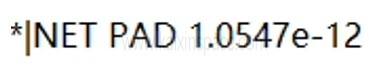

如果对应网表中无法获得,可以使用工具仿真得到,如下图。

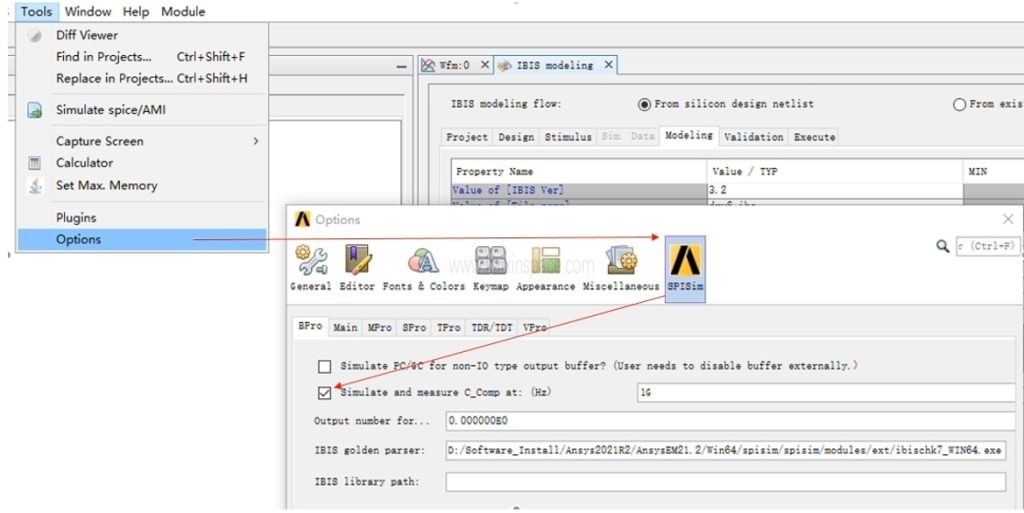

3.3.5 在Validation选项中,按如下图设置,全选需要验证的数据;

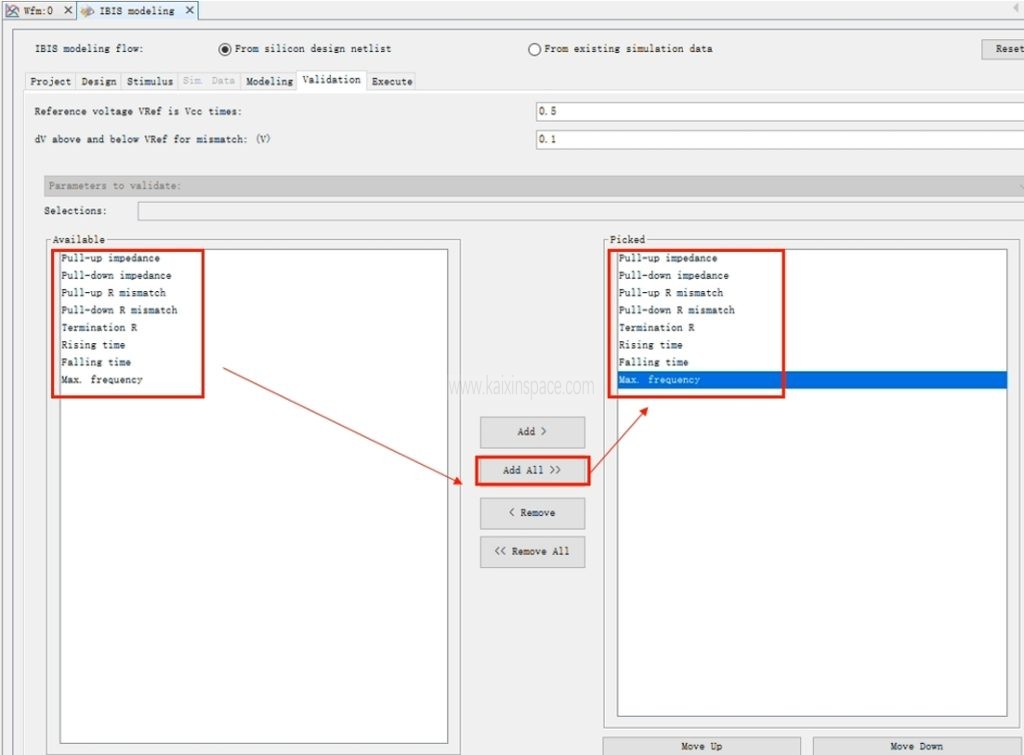

3.3.6 在Execute选项中,按步骤0-7完成操作即可。

提示:在执行完每一步时都会对应生成相关的数据,如下图,当某一步骤出现问题时,我们可以点击Checker Log进行查看相关问题。

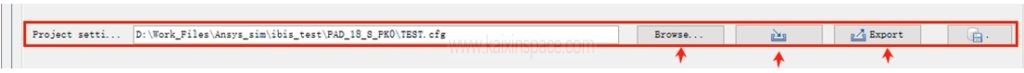

最后将上述配置好的数据进行保存生成.cfg,方便下次导入。

至此,一个完整的子模型IBIS生成完毕。其他子模型同样方式操作即可。

4. 问题与讨论

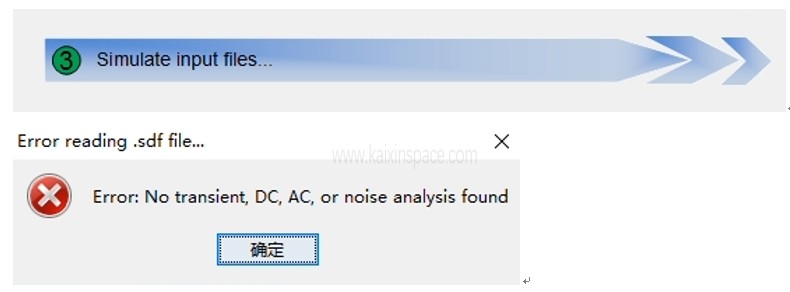

4.1 如果3.1中的说明未正确被设置,那么可能会出现什么样子的错误提示呢,如下是笔者遇到的,请参考。

Ans:当SPISim运行时将出现如下错误。

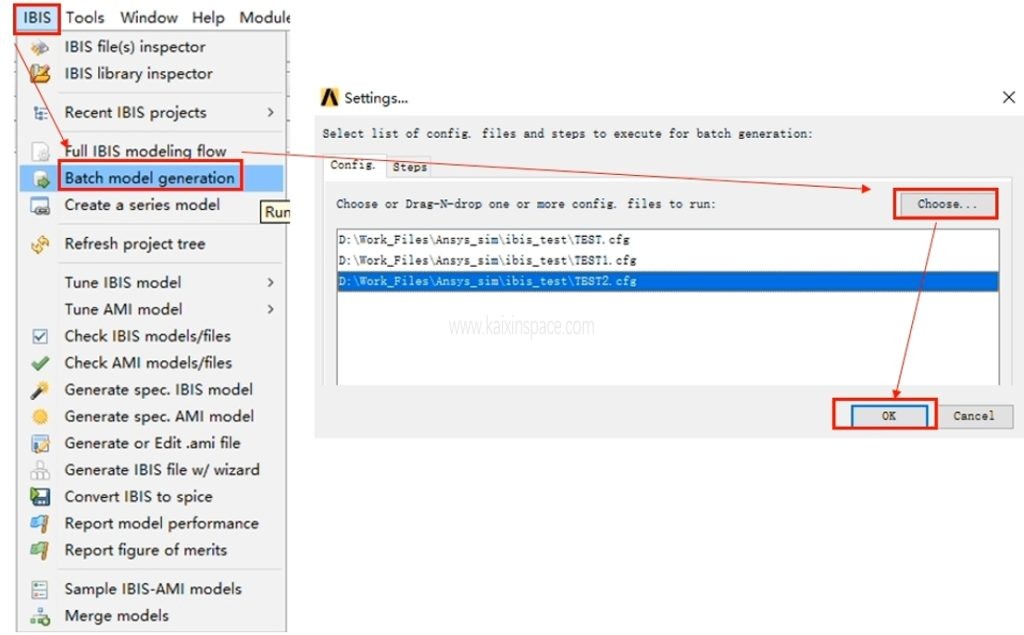

4.2 在3.2.3节中,有很多子模型,如何设置可以一次仿真多个子模型呢?

Ans:可以根据需要的模型参数对模型进行分别配置并生成对应的.cfg文件,这样可以使用如下图片所示功能一次性跑多个.cfg文件。这样可以大大加快仿真速度。

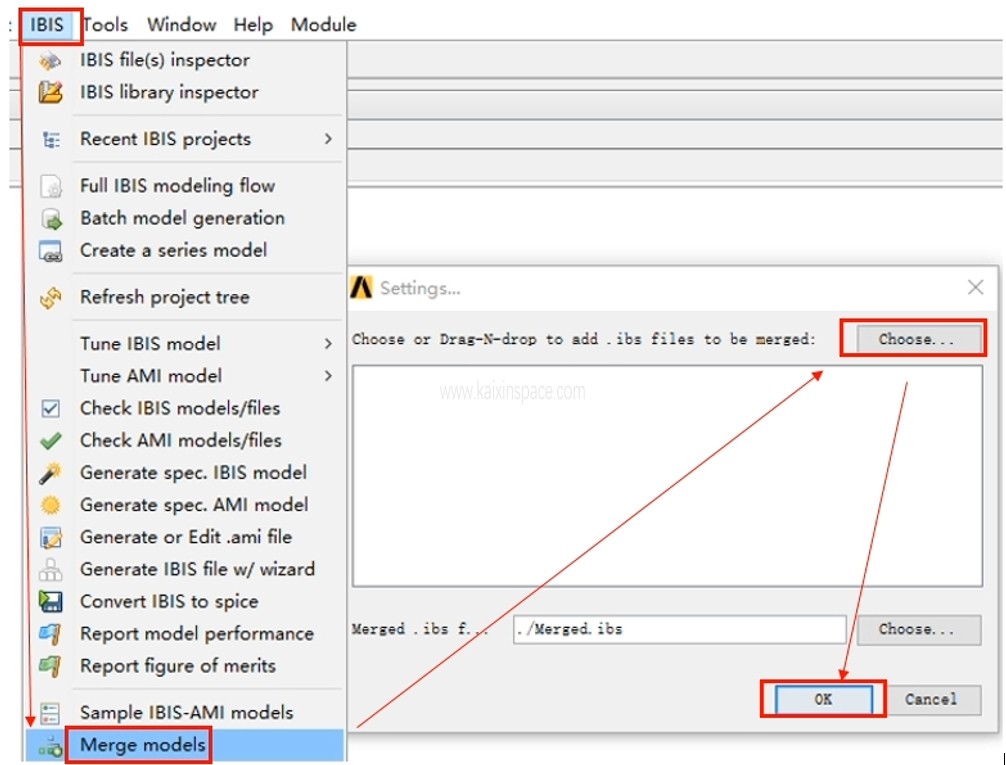

4.3 生成的多个子IBIS模型数据如何合并到一个IBIS模型数据中?

Ans:菜单栏选择IBIS-merge models,如下图;

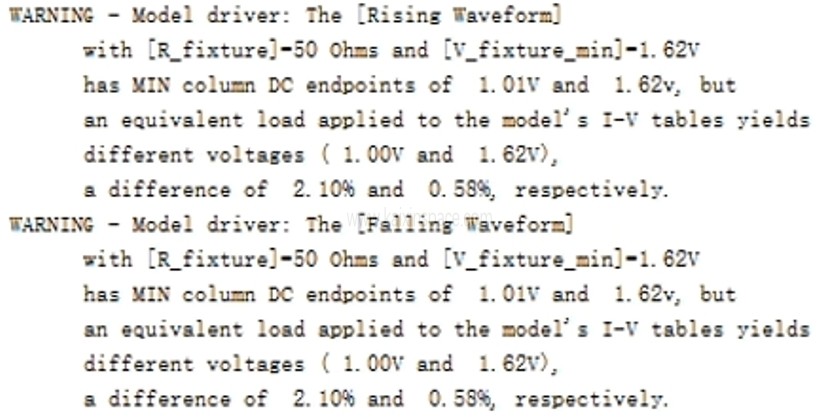

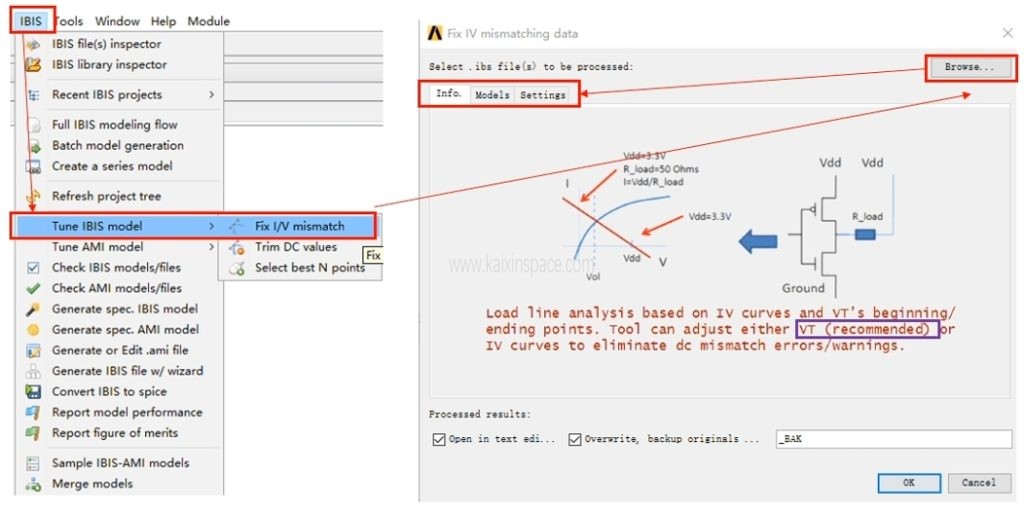

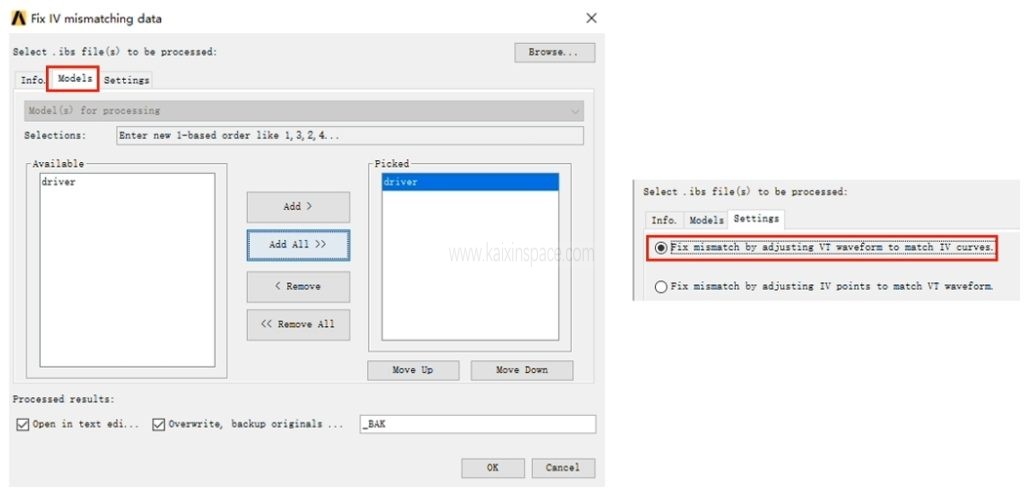

4.4 生成模型在做check时出现如下warning时,如何消除这些警告呢?

Ans:菜单栏选择IBIS-Tune IBIS model,如下相关图片。又或可以参考如下文章链接:

緩沖器模型: IBIS模型的除錯及效能調校 | SPISim[使必信科技]: 信號完整性、電源完整性暨電路擬真軟體

5. Reference