本文始于2024年01月,以2024R1 Siwave CPA(Chip Package Analysis)讲解如何抽取Wirebond封装相关的寄生参数,并导出成IBIS 2.0格式。

1. 封装相关资料和参数准备

1.1 对应需要导入的封装设计文件,xxx.sip格式

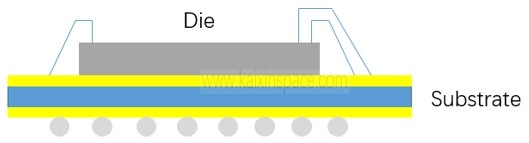

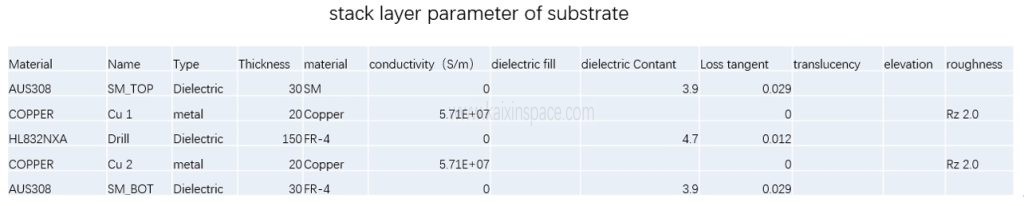

1.2 Substrate相关叠层信息和叠层中使用的材料参数,如:Cu的导电率、介质的介电常数和介质损耗等等。(对应叠构图和材料参数)

1.3 Bondwire 相关参数

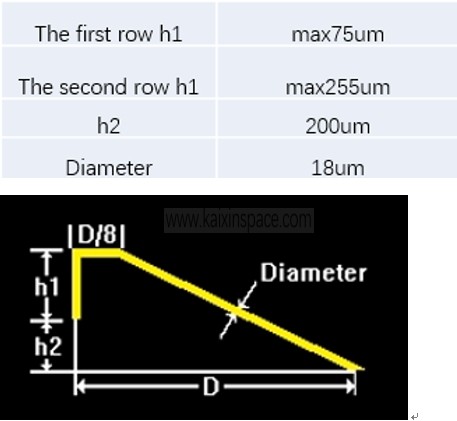

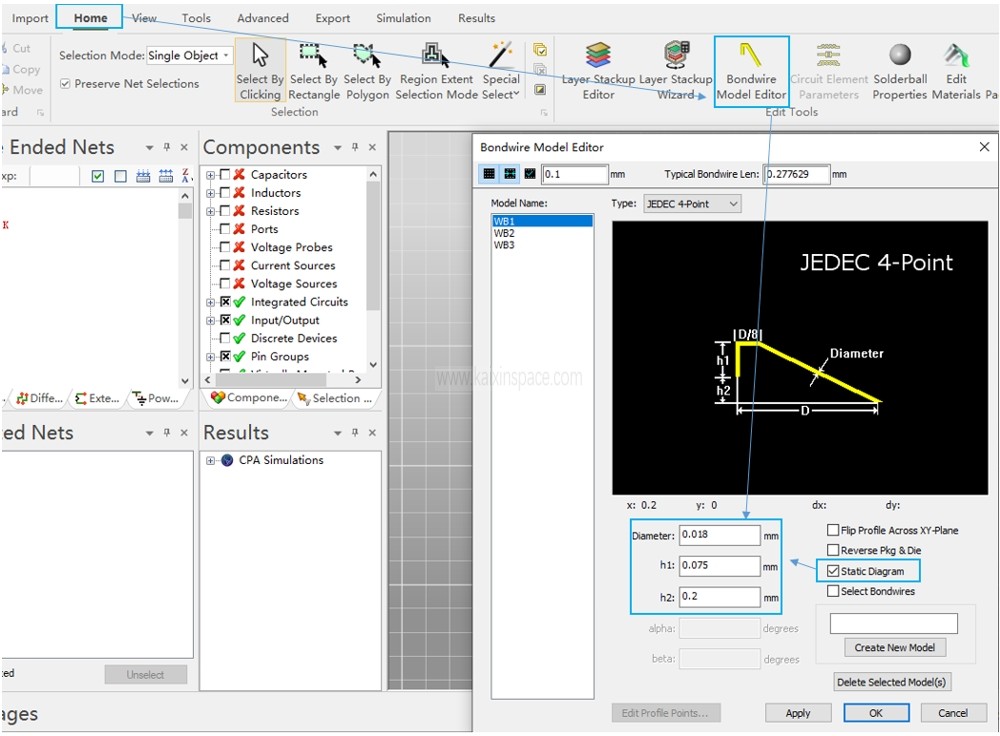

由于我们这里使用的WB封装是有两排的bondwire(如1.2节中叠层图所示),所以这里会有两排参数,如下图:

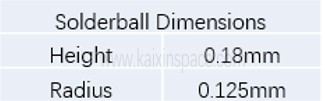

1.4 Solderball相关参数

2. 相关操作

2.1 导入对应的TEST.sip文件

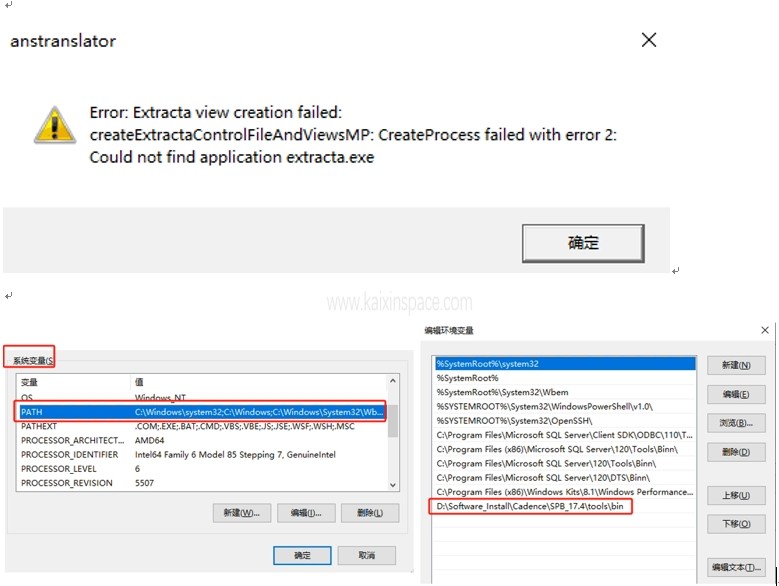

说明:Siwave现在不支持直接导入Sip文件,需要先从Ansys Electronics Desktop 导入,如果对应导入出现如下错误,需在系统环境变量path路径中增加对应Extracta.exe文件的位置。(Extracta.exe文件为安装cadence软件时安装的程序文件)

说明:电脑上只有安装cadence软件才能导入对应文件到ansys软件中。

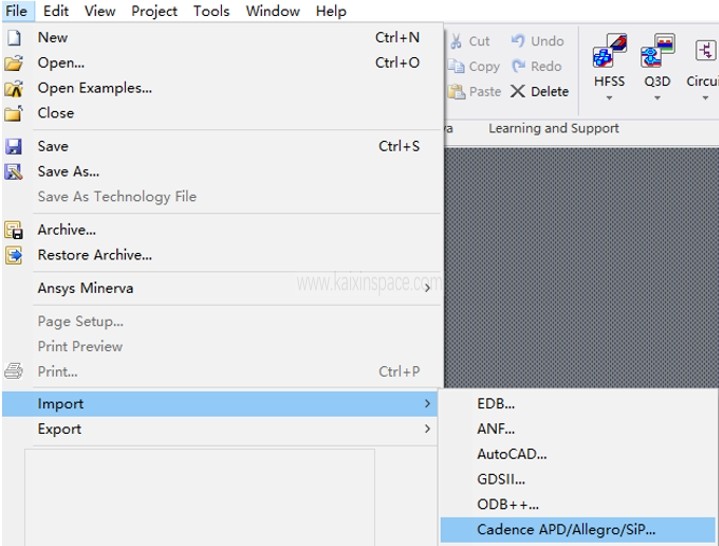

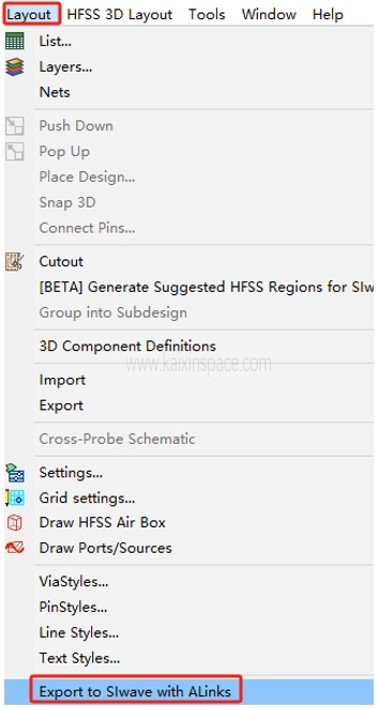

首先打开Ansys Electronics Desktop软件(以下简称:AEDT),菜单栏File-import-Cadence APD/Allegro/Sip..,导入后在AEDT对应菜单栏选择Layout-Export to siwave with alinks即可,如下图。

2.2 在Siwave软件中设置相关参数。

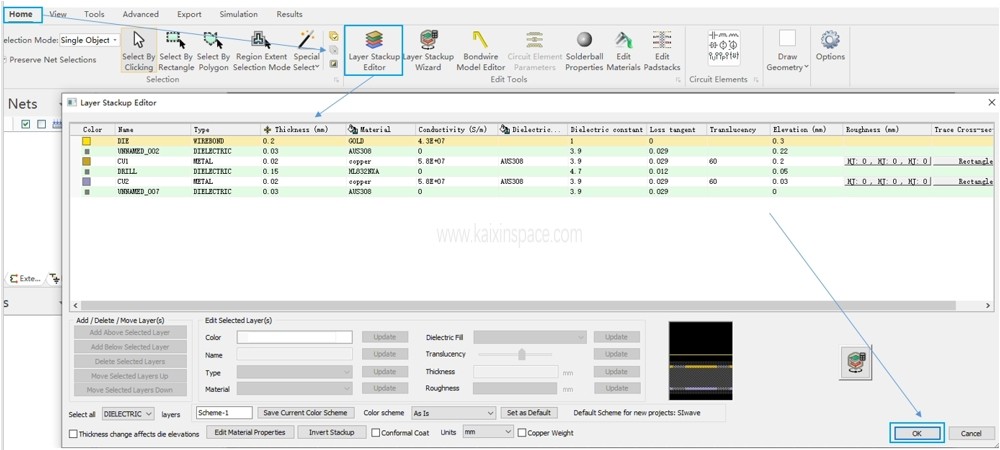

2.2.1 叠层结构和材料参数设定,如下:

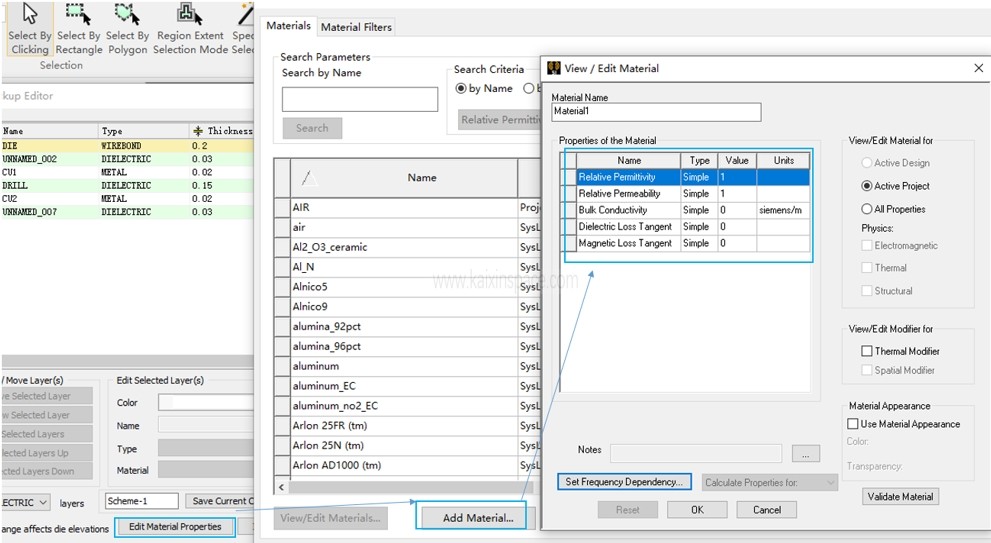

对应新的材料可以按如下方式添加新材料以及对应的材料属性。

2.2.2 bondwire 参数设定,也可以点击create new model 新建WB模型。

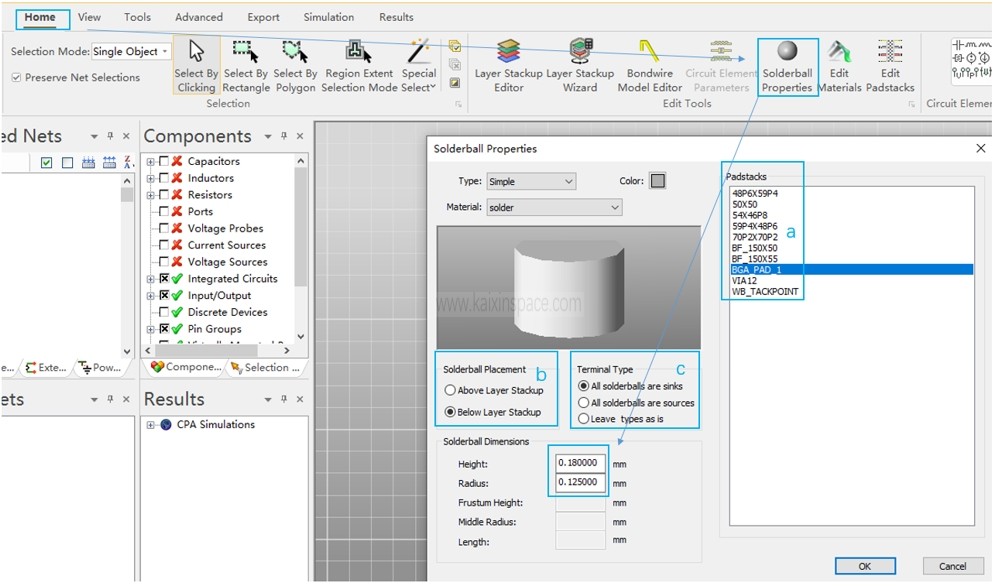

2.2.3 Solderball 参数设定

- 选择正确的pad,来生长锡球;

- 选择生成锡球的方向,Above Layer Stackup,表示向上生长锡球(Filpchip),Below Layer Stackup 表示向下生长锡球;

- 选择正确的Terminal 类型,这里设定solderball为sink。

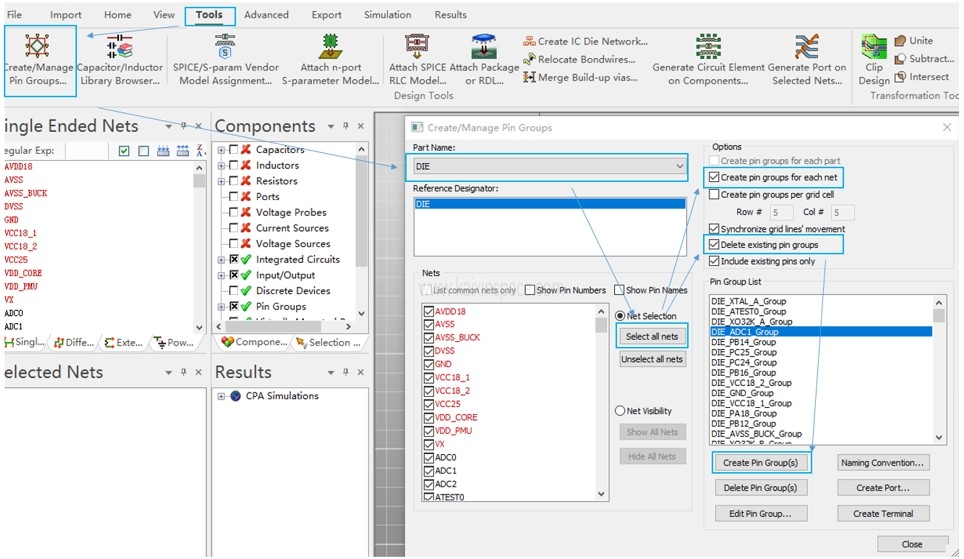

2.3 设置Die和BGA端的pin group

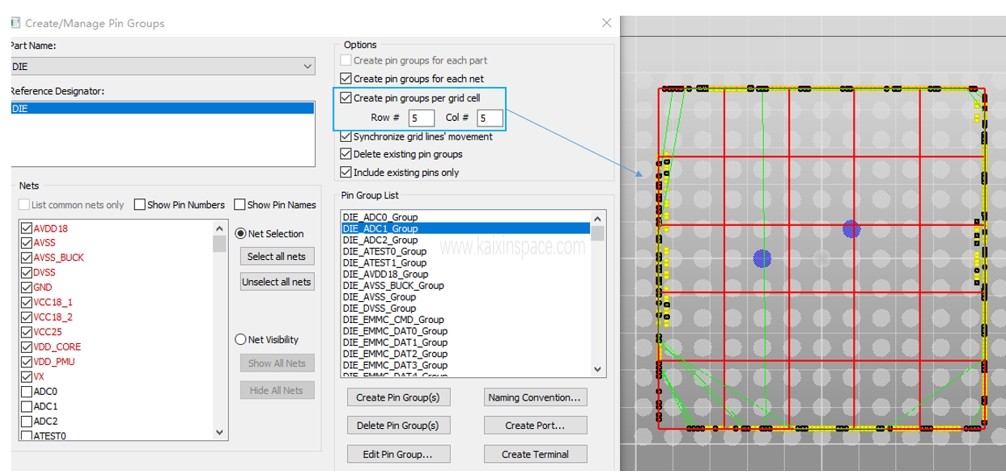

2.3.1 Die端pin group

同理按上图同样设置BGA端的pin group。

这里说明下,siwave 也提供了按网格来生成pin group,如果有需要可以勾选Create pin groups per grid cell选项。

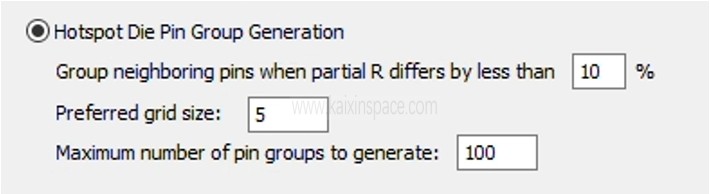

另外:在CPA仿真设置界面还提供了在die端自动生成smart pin group(Hotspot pin选项),会使得pin group 分配更合理。

注:不同的pin group方式使用者可以按需选择。

2.4 相关仿真设置

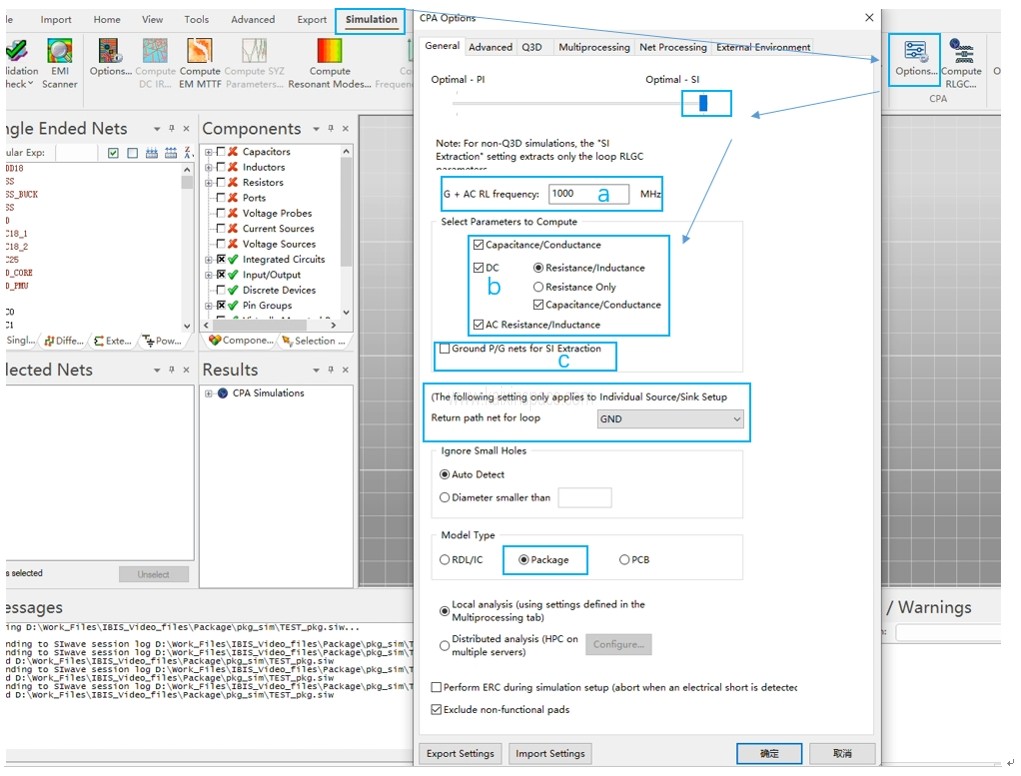

2.4.1 General 选项卡

- 表示需要求解的频率;

- 请将AC和DC都勾选上,因为求解相关RLGC参数时会同时用到DC和AC的值;

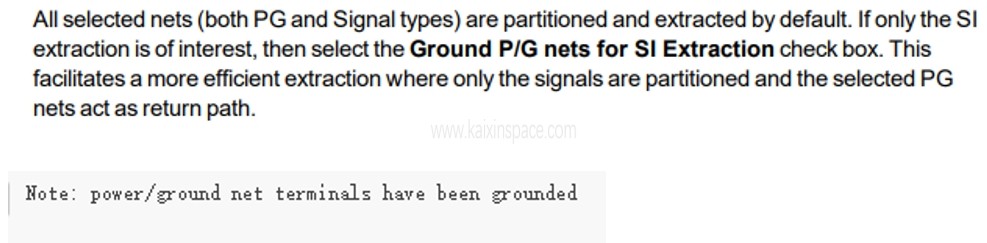

- 表示电源和地网络短路到一起作为信号回流路径;

实际使用中不建议勾选此项,因为软件中认为ground net 为理想的电压为0,没有RLC寄生,这违反实际情况。

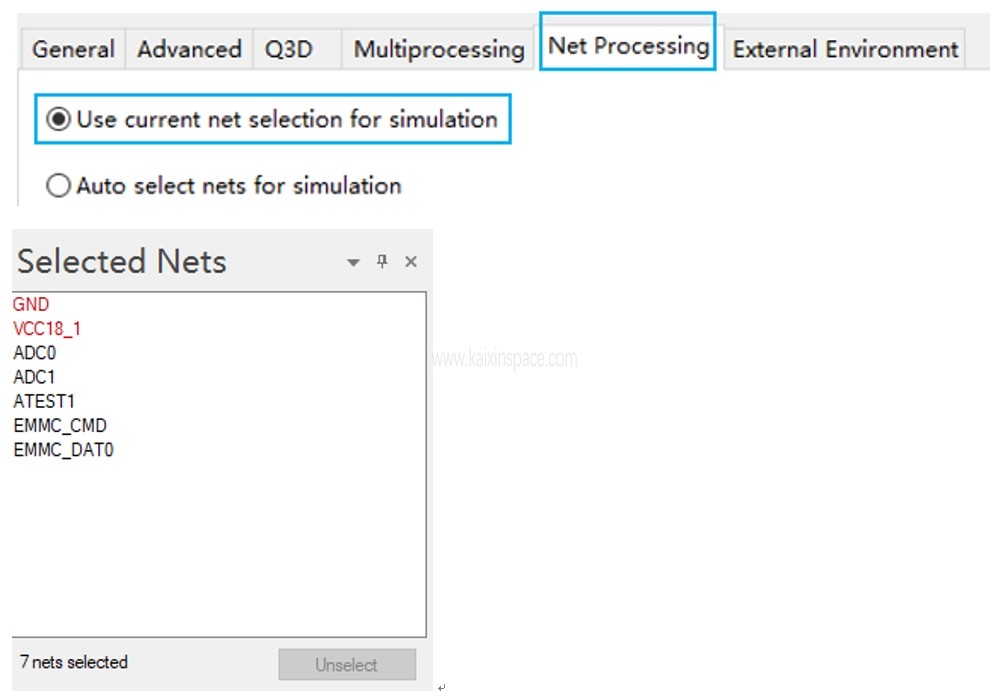

2.4.2 Net Processing 选项卡;

选择对应的求解的net进行求解。

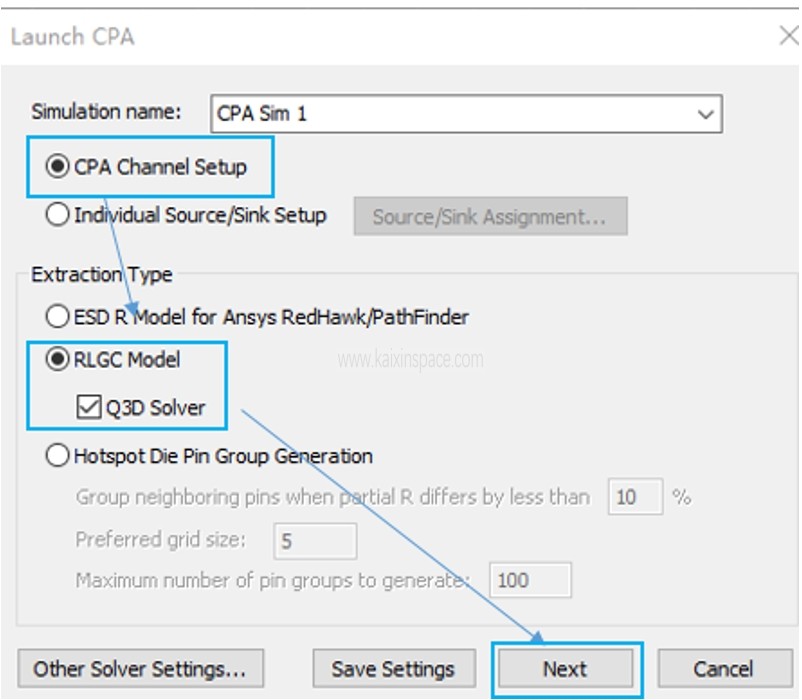

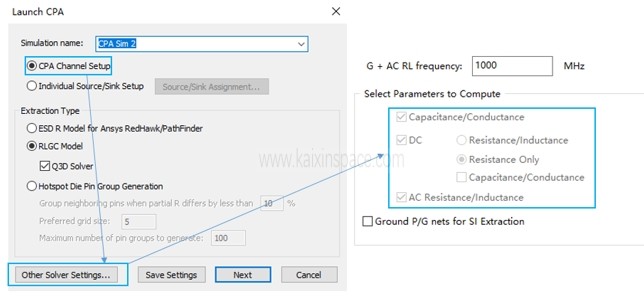

2.4.3 选择CPA模块中Compute RLGC..,

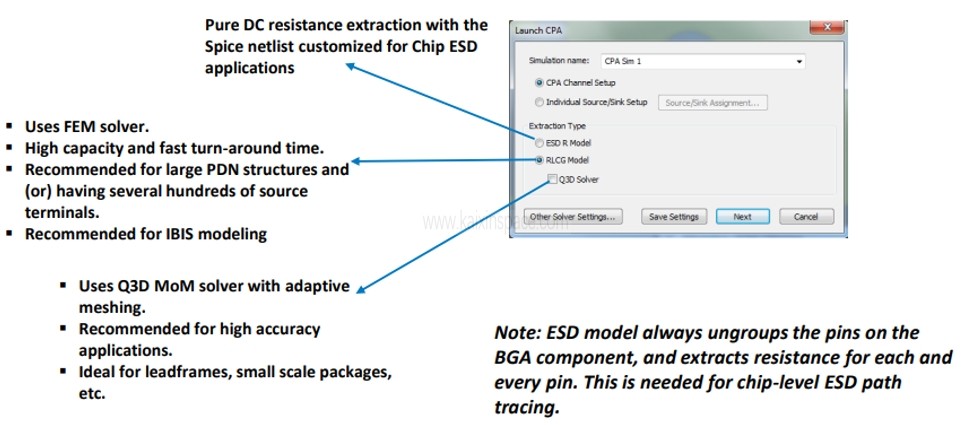

对应Extraction Type 可参考如下图片解释;

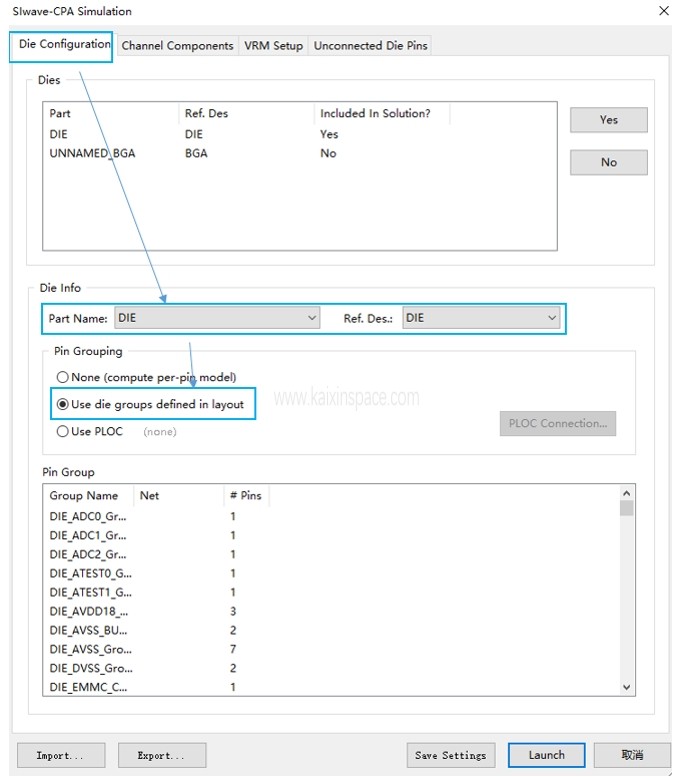

点击Next按钮,出现如下对话框,点击Die Configuration选项卡,按如下设置;

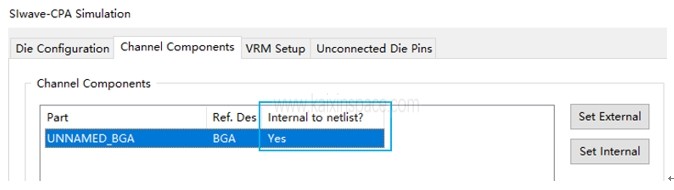

在点击Channel Components选项卡;

这里会显示first die和substrate之间的器件,如:substrate上的电容等都会在这里显示,如果需要单独提取这些器件的寄生参数,请将对应的Internal to netlist 设置 NO。

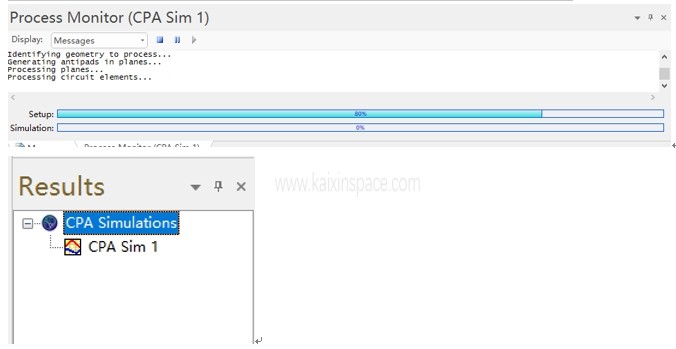

最后点击Lanuch,开始求解,求解完成会在Results栏中出现对应的结果。

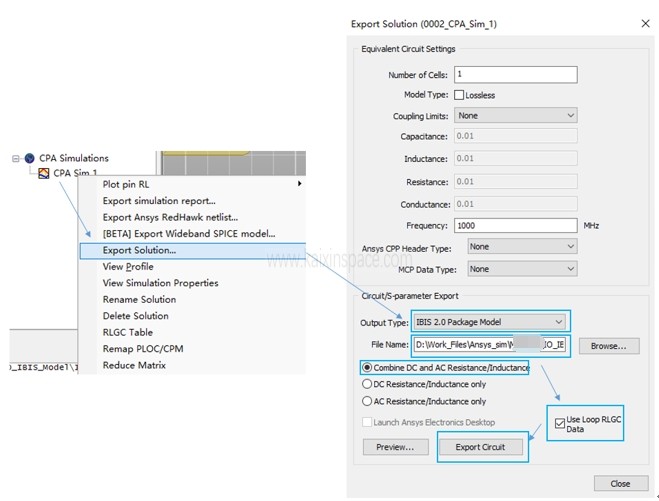

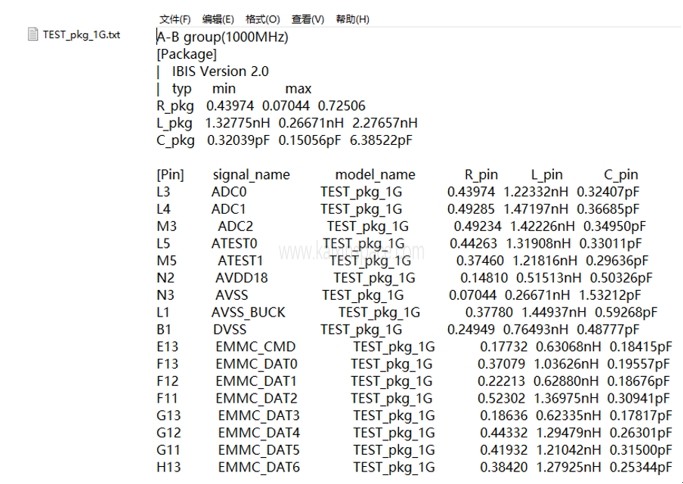

2.5 根据对应的求解结果导出对应封装寄生参数RLGC模型

至此,Wirebond封装寄生参数模型(IBIS封装模型)提取完成。

3. 问题与讨论

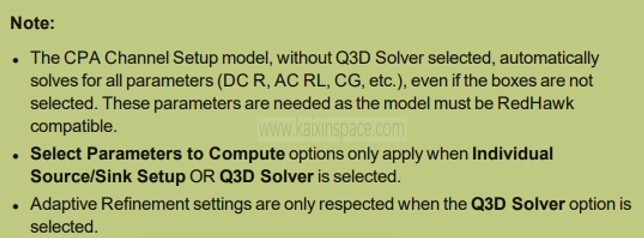

(1)为何在CPA仿真设置中选择CPA Channel Setup时,在点击Other Solver Settings… 弹出的对话框中的Select Parameters to Compute一栏是不可选的呢(显示灰色)?

Ans:请参考如下help中的说明。

另外请注意:当选择CPA Channel Setup时,default软件默认只选择DC R,而DC L和 DC CG是没有选择的,所以如果用户希望解DC L和 DC CG时,请到CPA模块栏选择单独Option选项进行设置即可。

-END-