本文始于2024年06月,主要介绍电源完整性相关的基础知识和一些关键点,同时文章中也介绍了几种定义目标阻抗的方法,供大家参考。

1. 电源完整性概述

1.1 什么是电源完整性

1.2 电源纹波与噪声

3. 电源分配系统(Power Distribution Network—PDN)

3.1 PDN组成

3.2 电容频率特性及去耦电容解释

3.3 电感重要性

4. 目标阻抗

4.1 自阻抗和互阻抗

4.2 得到目标阻抗的几种常见方式

5. 时域分析

6. 参考

1. 电源完整性概述

1.1 什么是电源完整性

电源完整性是电子系统中确保电源传输和电源分配网络能够提供稳定和干净电源,是能够满足负载芯片对电源的供电要求,并且提供低阻抗和低噪声的信号返回路径。

1.2 电源纹波与噪声

电源纹波是由开关电源在转换过程中产生的周期性电压波动。其主要原因是电源的开关频率和内部元器件的特性。纹波通常表现为固定频率的波动,其幅度和频率取决于电源设计和负载情况

电源噪声是电源供应中不规则的、高频干扰信号。噪声可以来自于外部电磁干扰、瞬态电流变化、PCB布局不良等。

电源纹波和噪声的危害主要有以下几个方面:

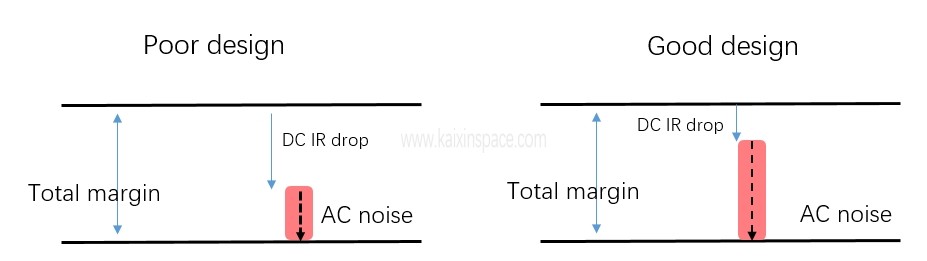

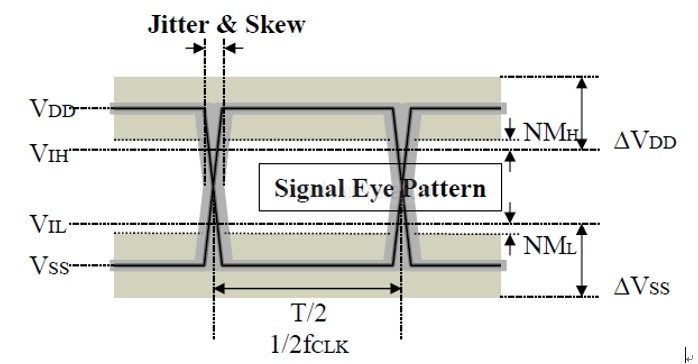

① 噪声容限变小;

② 时序容限变小、数据相移/抖动;

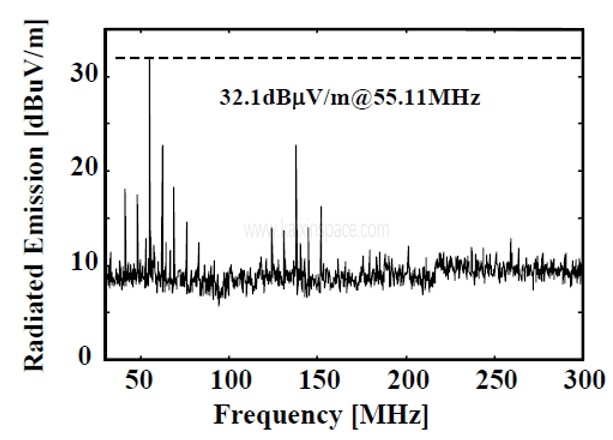

③ EMI增大

2. 电源波动组成和电源噪声的主要来源

2.1 电源波动组成

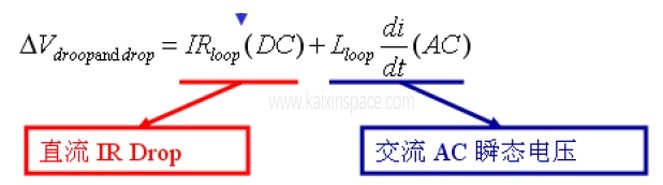

DC损耗+AC噪声

2.2 电源噪声的主要来源

- 稳压电源芯片本身的输出并不是恒定的,本身就会有一定的纹波;

- 稳压电源无法实时响应负载芯片对于电流需求的快速变化,造成电压跌落;

- 电源路径和返回路径上存在一定的阻抗,负载瞬态电流变化产生压降;

- SSN(Simultaneous Switch Noise)同步开关噪声。

3. 电源分配系统(Power Distribution Network—PDN)

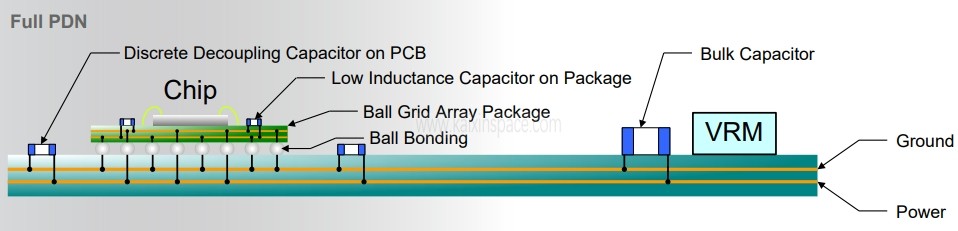

3.1 PDN组成

- VRM(Voltage Regulator Module)电源芯片;

- PCB(Printed Circuit Board )上的电容;

- PCB上的电源和地平面;

- 封装内基板(substrate)上的电容;

- 封装内基板上的电源和地平面;

- 芯片die里的电容

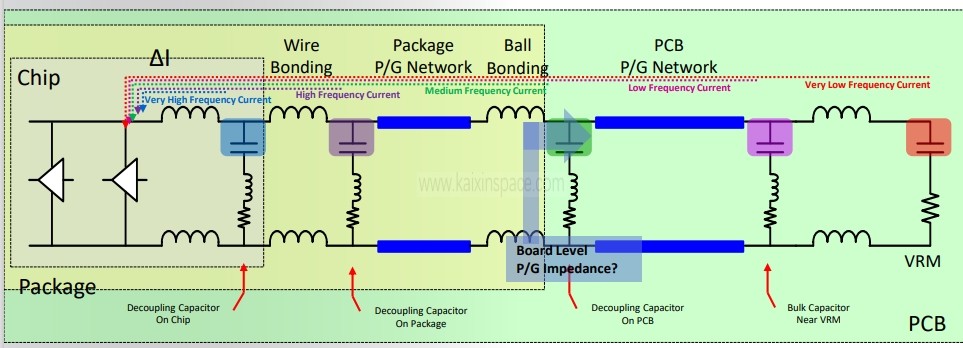

对应的PDN电路简化模型如下:

从VRM到IC端,整个PDN网络分为PCB板级、package封装级、IC级,其去耦电容的频率依次提高;

一般情况下,板级的去耦电容能作用频率到百赫兹,在往上就需要封装内的电容(数百兆赫兹),在往上就需要靠IC内的电容。

3.2 电容频率特性及去耦电容解释

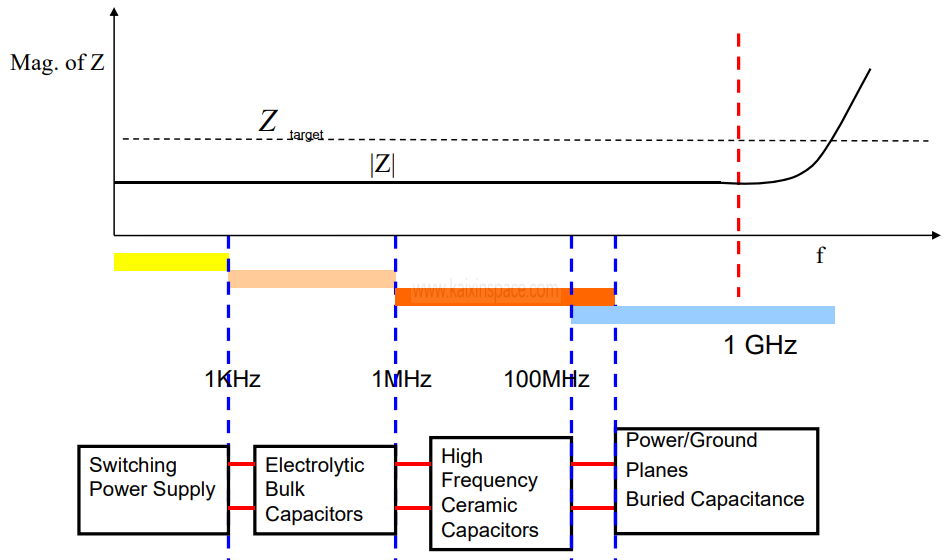

- 电容频率特性

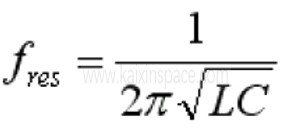

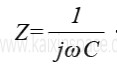

理想电容阻抗公式:去耦电容的阻抗与频率相关,阻抗随频率增加而减小。

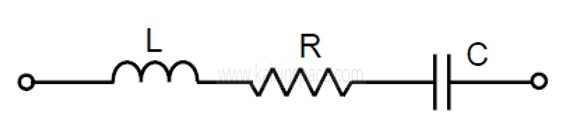

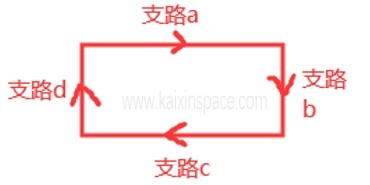

一个真实的电容包含一些重要的寄生参数,如等效串接电感(ESL-Equivalent Series Inductance)和等效串接电阻(ESR-Equivalent Series Resistance)

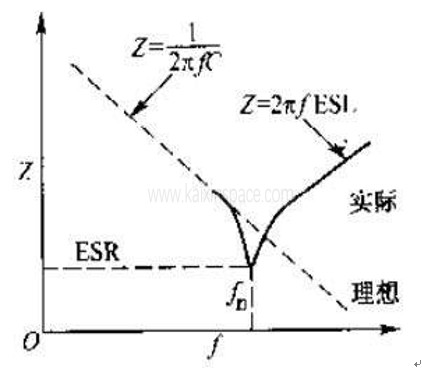

如上图,电容在高频等效后的电路会在某个频率处谐振,这个频率称为自谐振频率,当电容作为去耦电容时,应使其工作在自谐振频率附近。公式如下:

- 去耦电容解释

在电源分配网络(Power Distribution Network,PDN)中,去耦电容具有两个主要功能:储能和降低阻抗。

(1)储能角度

从储能角度来看,去耦电容的主要功能是提供一个局部的能量储备,以应对瞬态电流需求和减少电源电压波动。

储能特点:

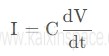

- 瞬态响应:当负载突然增加或减少时,去耦电容可以快速释放或吸收电荷,提供或吸收瞬时电流,从而保持电压的稳定。这是因为电容器能够在极短的时间内放电或充电。

- 平滑电压:通过在电源和地之间放置去耦电容,可以平滑电压波动,减少电源噪声和尖峰。这对于高速数字电路尤其重要,因为这些电路对电源波动非常敏感。

- 局部储能:去耦电容直接放置在电源引脚附近,可以就近提供电流,减小电源轨上的电流波动,减少电源线上的电压降。

相关公式及电路简化示意图:

(2)阻抗角度

从阻抗角度来看,去耦电容的主要作用是降低PDN的阻抗,以确保在各种频率下都有足够低的阻抗,满足电路的动态电流需求。

阻抗特点:

- 频率响应:去耦电容的阻抗与频率有关,阻抗随频率增加而减小。在高频下,电容的阻抗很低,可以有效滤除高频噪声和干扰。

- 多层去耦:在实际电路设计中,通常会使用多个不同容量值的去耦电容组合,以覆盖更宽的频率范围。小电容值(如0.01μF或0.1μF)用于高频去耦,大电容值(如10μF或100μF)用于低频去耦。

- 降低谐振:通过在不同位置放置去耦电容,并选择不同的电容值,可以避免在某些频率上产生谐振,从而保持较低的阻抗。多个电容组合可以形成一个宽频带的低阻抗特性。

相关公式和等效电路如下:

3.3 电感重要性

3.3.1 回路自感

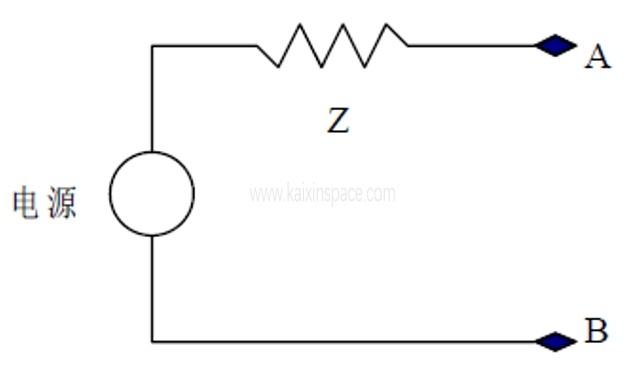

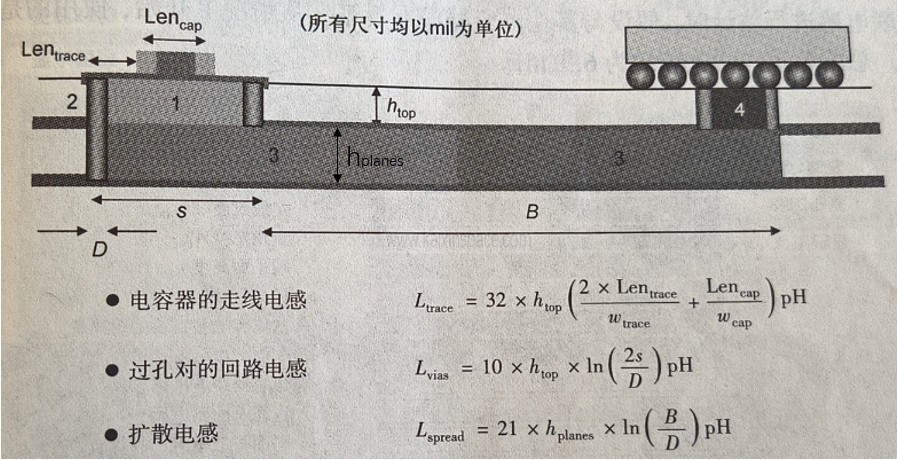

如下为最常见互连的结构等效图(为简化说明不考虑其他路径互感)。支路a充当信号路径,支路c充当返回路径,支路b、d充当导通孔。

L(loop)=La-Lac+Lc-Lca+Lb+Ld= La+ Lc+ Lb+Ld-2Lac

其中,L(loop)表示整个回路自感,La表示支路a的局部自感,Lb表示支路b的局部自感,Lc表示支路c的局部自感,Ld表示支路d的局部自感,Lac表示支路a和c之间的局部互感。

上式表明两个支路靠得越近,回路电感就越小。其中各支路的自感保持不变,而互感增大,互感增大使各支路周围的磁力线总匝数减小,从而使回路自感也减小了。

3.3.2 电容安装电感

上面介绍了电容自身的参数,然而当电容安装到电路板上之后,还会引入额外的寄生电感参数,从而引起谐振频率的偏移。

电容在电路板上的安装通常包括一小段从焊盘拉出的引出线和周围两个或多个过孔。然而实验表明电容的安装电感会对电容的去耦特性有影响,所以要尽量减小。

3.3.3 回路自感和电容安装电感优化

(1)减少从电容焊盘到过孔之间的走线回路电感,有如下3个因素可以调节:

- 表层到电源/地平面对的高度要短(htop);

- 表层走线要尽量宽(wtrace);

- 表层走线尽量短(Lentrace);

(2)减少过孔电感,有如下3个因素可以调节:

- 表层到电源/地平面对的高度要短;

- 过孔孔径加大;

- 不同网络之间过孔尽量接近;

(3)减少平面的回路扩散电感,有如下3个因素可以调节:

- 电源/地平面对之间的介质厚度要薄;

- 过孔孔径加大;

- 将电容器尽量靠近被去耦的芯片附近。

4. 目标阻抗

4.1 自阻抗和互阻抗

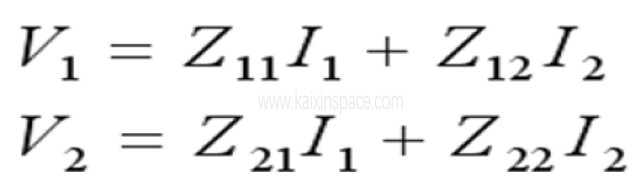

这里以两端口网络说明,如下图:

其中:

Z11、Z22——自阻抗或称输入阻抗;

Z12、Z21——互阻抗或称转移阻抗;

对于是N端口网络的阻抗可以写成如下公式:

Vn=Zn1*I1+Zn2*I2+…+ZnN*IN

在实际项目中存在如下两种场景:

场景1:不同的IC芯片供电,用同一个电源网络。

对于评估系统中关键IC芯片电源性能,在某些情况下(特别是系统中存在大电流)需考虑互阻抗;

场景2:一颗IC芯片中存在多个相同电源pin管脚。

对于评估IC中某个关键pin引脚的供电性能,同样需要考虑互阻抗。

注意:信号的返回路径和信号路径同等重要,不要忘记对gnd路径的优化。

另外请时时刻刻记住如下两条基本定律:

(1)电流永远都是一个回路;

(2)电流总是流向阻抗最低的通路。

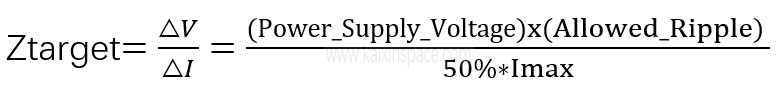

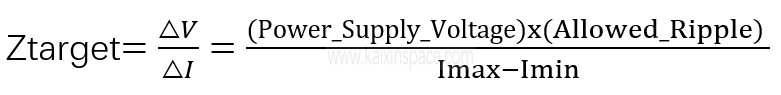

4.2 得到目标阻抗的几种常见方式

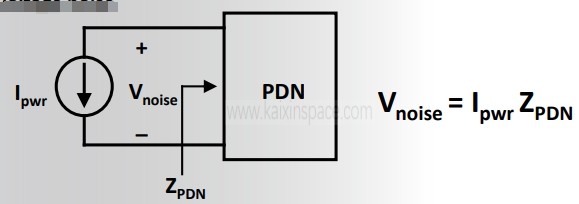

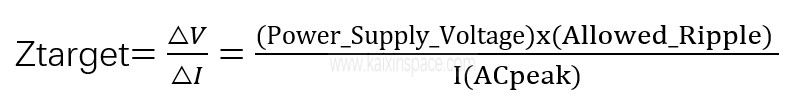

目标阻抗是为满足特定电路对电源稳压和噪声抑制需求而设定的最大允许阻抗值(随频率变化)。

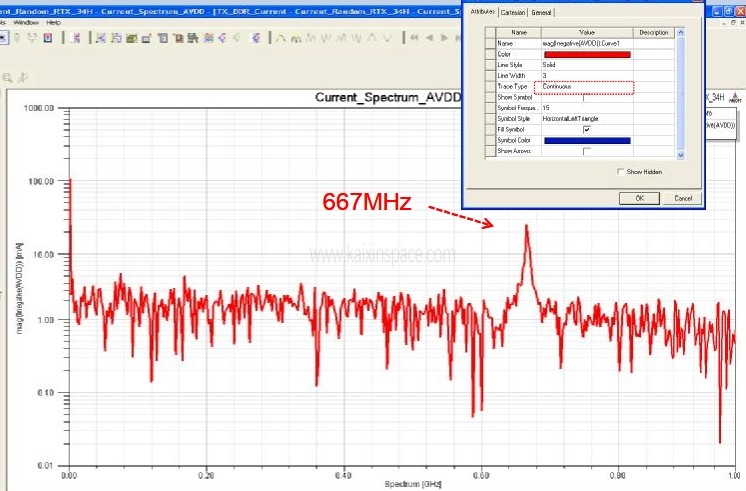

第一种:透过仿真的方式得到相关目标阻抗

在实际项目中,首先确定需要分析的电源网络,然后取得相关器件的模型(IBIS或其他类型模型),仿真得到相关电源的电流波形,如下图;

对上述得到的电流波形做FFT,得到对应频谱,如下图;

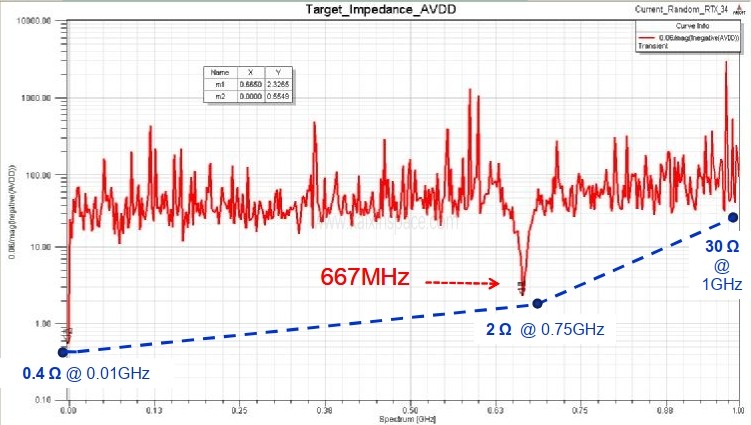

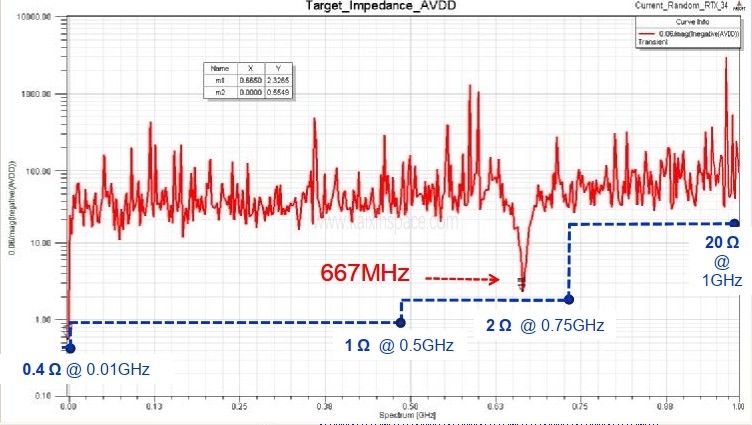

最后将容许的电压噪声除以对应的电流频谱,得到对应的阻抗曲线图,如下图;

或

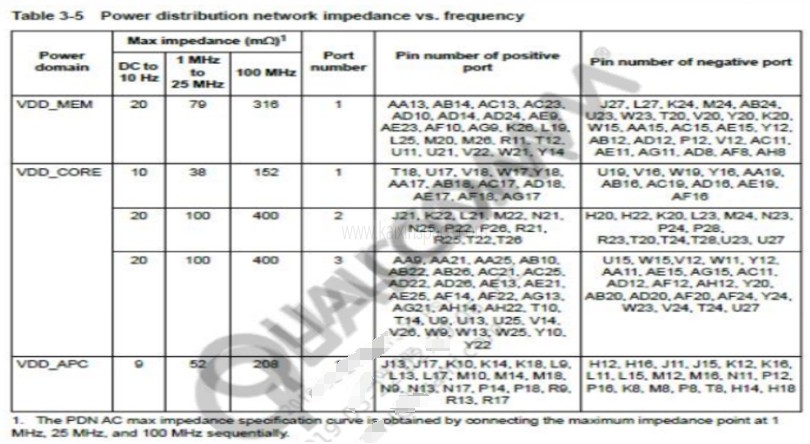

第二种:由芯片厂商在对应手册规格书中给出具体值,如下图;

第三种:

第四种:

第五种:

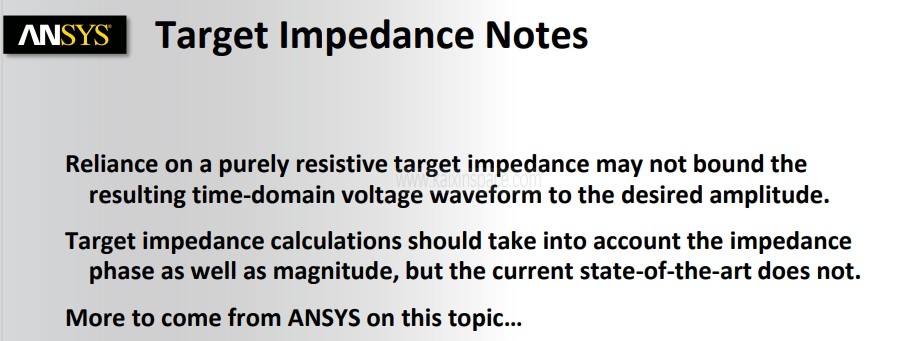

提醒1:目标阻抗不是定律也不是规范,只是为PDN设计分析提供一种有用有效的指导。

提醒2:上述几种方式估算的目标阻抗并未考虑电压和电流之间的相位关系,然而电压和电流之间的相位关系会影响到时域波形的幅度,故在PDN进行频域分析完后,一定要进行时域的波形验证。

5. 时域分析(Time Domain Analysis)

研究对象:研究电源或信号实际的波形,与激励信号有关,适用于观 测系统的有源、非线性特性;

优点:

- 直观性强:时域分析直接展示了电路或系统随时间变化行为,如电压、电流的波形,便于理解和分析。

- 瞬态响应分析:可以分析系统的瞬态响应,了解在输入信号变化或开关操作时系统的动态行为,例如开关电源的启动过程、信号传输中的反射和衰减等。

- 非线性系统分析:时域分析可以处理非线性系统。

缺点:

- 频域信息缺失:时域分析难以直接提供频域信息,如谐波成分、频谱分析等。频域信息对理解滤波器、调制信号和频率响应等问题至关重要;

- 计算复杂度高:对于复杂系统,时域分析的计算复杂度较高,尤其是在进行长时间仿真时,需要较长的计算时间和大量的计算资源;

- 受限的频率范围:不容易发现和解决问题, IC器件的电流激励I-t波形难以得到 ,测量容易受外部噪声的干扰;

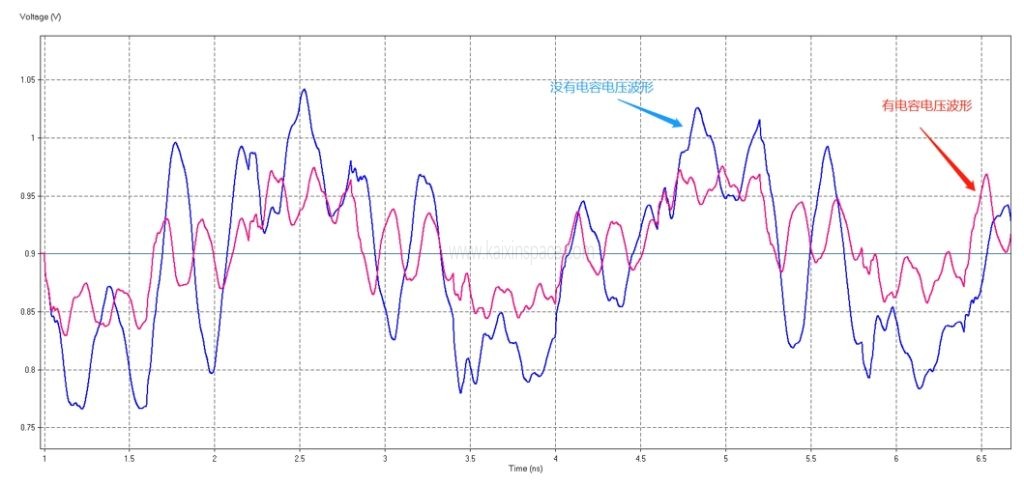

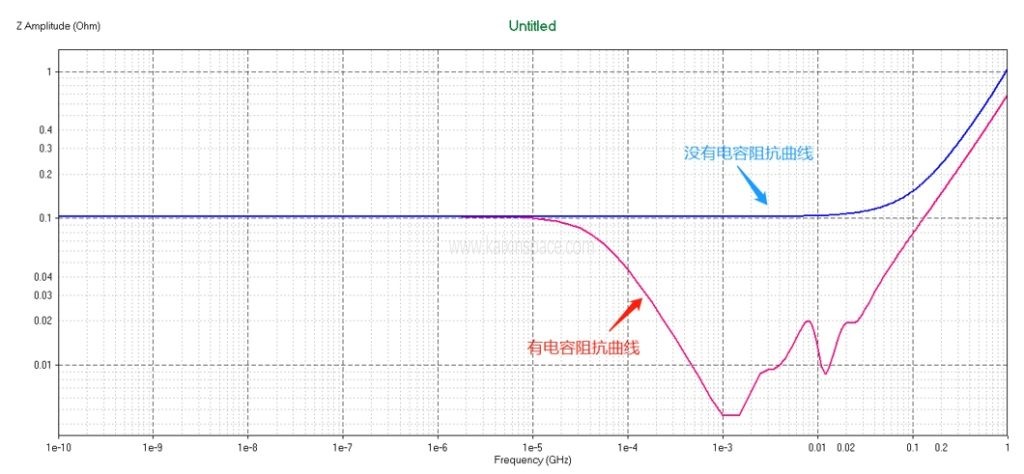

时域仿真中有电容和没有电容波形对比,如下图;

对应频域中Z阻抗曲线,如下图;

从以上两个图可以明显看出:频域阻抗好的曲线,在对应时域中电压波形波动明显会改善很多。

6. 参考

【1】信号完整性与电源完整性分析(第二版)—【美】Eric Bogatin著,李玉山等译;

【2】Ansys Chip-AwarePower integrity—Greg Pitnersaac Waldron 2019;

【3】Ansys Siwave 5.0 Pl Advisor forOptimized DDR3 MemoryDesign—Presented bySergey Polstyanko, Ph.DSenior R&D Manager 2010;

【4】Target Impedance and Rogue Waves Panel discussion-Eric Bogatin, Teledyne LeCroy, moderatorIstvan Novak, OracleSteve Sandler, PicoTestLarry Smith, Qualcomm Brad Brim, Cadencethe empty chair, in memoriam Steve Weir,DesignCon 2016;

【5】Case Studies lsolating Types of Power-ntegrity Effects on Signal Integrity, and Means of Mitigation-Nitin Bhagwath (Mentor Graphics, A Siemens Business)Rula Bakleh, Scott McMorrow, lstvan Novak (Samtec Teraspeed Consulting) ,DesignCon 2019;

【6】 定義目標阻抗的電源完整性優化設計(https://www.oldfriend.url.tw/);

【7】高速电路电源分配网络设计与电源完整性分析—张木水.