1. 什么是匹配?

在芯片制造过程中,因为一些系统误差和一些随机误差,使得实际生产出来的器件参数和实际理论参数存在一定的偏差,然而我们可以通过电路设计或器件布局或走线等相关措施(也就是匹配),使这种偏差减小到最小。换句话说,就是使器件对引起偏差的各种原因不敏感。

偏差大小排序:从大到小依次排列如下:

- 每批次与每批次之间(lot to lot)

- 每片晶圆与每片晶圆之间(wafer to wafer )

- 晶粒与晶粒之间(die to die)

- 器件与器件之间(device to device)

电流差异可能达到:5-30% ; 电压差异可能达到:10-100mV

如果想生产出来的器件更准,那就需要做校准(calibration),需要增加成本。

2. 影响器件匹配的一些因素

2.1 系统性失配(Systematic Mismatches)

这类失配因素主要包括:硅片应力梯度、封装应力、工艺偏差、互连寄生、刻蚀速率、扩散相互影响、介质极化等其他许多因素。

下面简单讨论下上述几种因素:

2.1.1 应力梯度

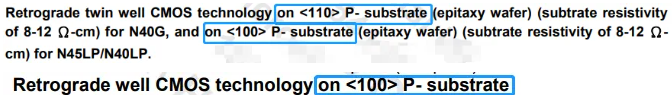

如下为:晶圆方向定义

- 对于MOS管来说:应力使载流子的迁移率发生变化,从而影响mos管器件的跨导。

在<100>晶圆体硅中,沿<110>晶轴方向上,由应力引起的电子体迁移率的变化量最小;而沿<100>晶轴方向上,由应力引起的空穴体迁移率变化量最小。

在版图中:

NMOS管中,电子是主要载体,所以nmos管水平或垂直(X轴或Y轴)摆放,可以使它们的应力灵敏度最小化;

PMOS管中,空穴是主要载体,所以pmos管与X轴或Y轴成45度摆放,可以使它们的应力灵敏度最小化;考虑实际情况,我们还是会沿X轴或Y轴摆放pmos,因此这也是nmos比pmos匹配的更精确的原因之一。

- 对于电阻器件来说:硅片的压阻系数随方向和掺杂的不同而不同。

在<100>晶圆体硅中,沿<110>晶轴方向上,N型硅片表现出最小的压阻系数,P型硅片表现出最大的压阻系数;而沿<100>晶轴方向上,N型硅片表现出最大的压阻系数,P型硅片表现出最小的压阻系数。

在版图匹配中:

N型硅电阻水平或垂直(X轴或Y轴)摆放,可以使它们的应力灵敏度最小化;

P型硅电阻与X轴或Y轴成45度摆放,可以使它们的应力灵敏度最小化;

Tips:不同工艺的规格书中会明确说明制作晶圆方向。

2.1.2 工艺偏差

硅片上生产出来的图形不会和版图数据的尺寸完全匹配,因为在光刻、蚀刻、离子注入等过程中图形会收缩或扩张。导致版图数据的尺寸和实际生产测量的尺寸之间存在偏差,简称:工艺偏差。

2.1.3 互连寄生

版图中的走线和过孔等,会带来寄生电容和寄生电阻。

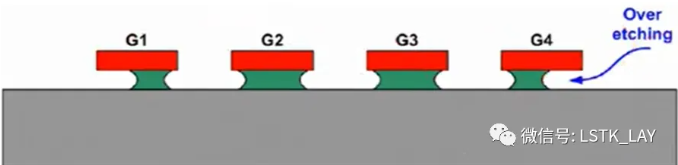

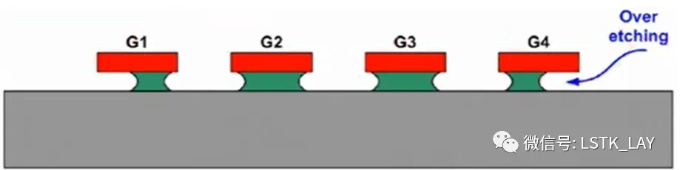

2.1.4 刻蚀速率

在一定程度上,刻蚀速率取决于多晶硅开口形状。大的开口可以进去更多刻蚀剂,会比小的开口刻蚀速度快。对大开孔边缘处侧壁侵蚀比小开孔的严重(over etching),这种效应会使开口大的多晶硅图形比紧密放置图形的宽度要小。

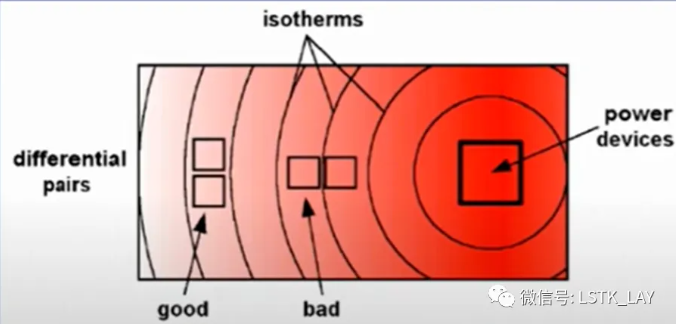

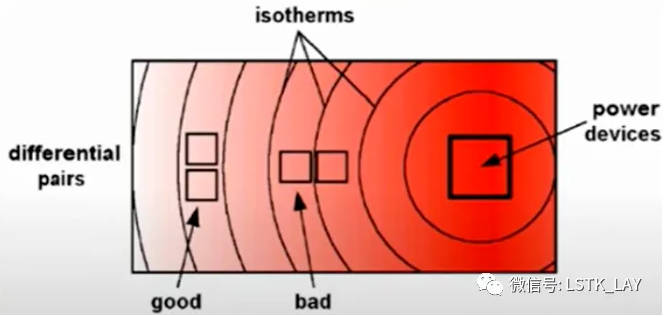

2.1.5 温度梯度

远离功率器件或模块,如果空间限制请使用共质心匹配。

2.2 随机失配(Random Mismatches )

这类失配因素主要包括:尺寸、掺杂、氧化层厚度、离子注入等其他原因。

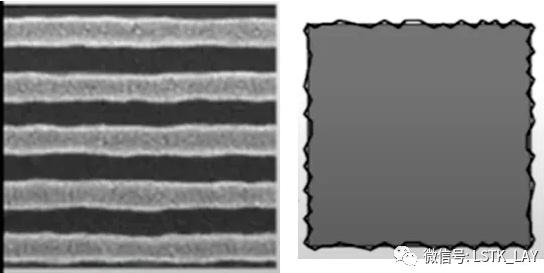

由于制造的一些误差实际周长尺寸和面积尺寸会有所改变。实际制造出来的线会有毛边。

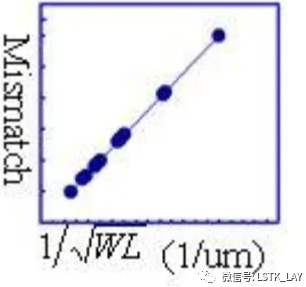

重点:尺寸越小,随机失配就越严重。有效减小随机失配办法就是增加mos管的栅极面积或其他类型器件的面积A(WxL)。

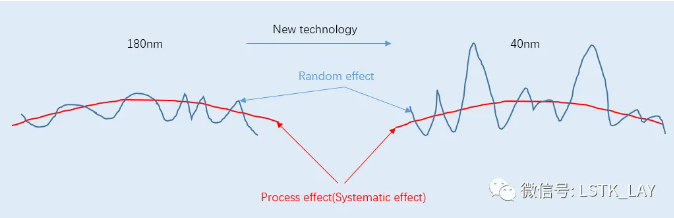

下图展示了工艺变化对随机失配的影响。

3. 实现匹配常见的方法

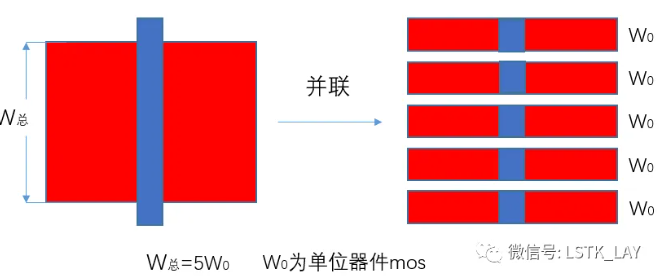

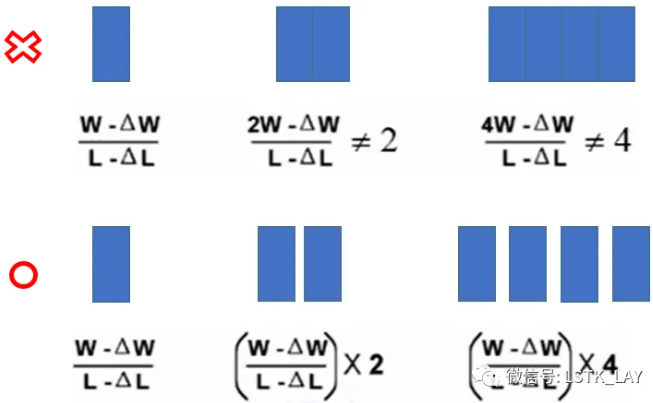

3.1.1 对于单个较大宽长比的mos而言,使用多个较小的宽长比的mos并联可以减小失配,这里较小的mos即为单位器件。

3.1.2 对于多个成比例需要匹配的器件而言,使用单位器件法,消除比例误差并减小失配。

3.2 叉指法(Interdigitated)

叉指法类似共质心中的一维匹配方式,其匹配原则同样类似共质心相关内容。具体请参考3.3节共质心描述。

3.3 共质心法(Common Centroid)

3.3.1 共质心的几个原则:

- 一致性(Coincidence):匹配器件的质心位置尽可能完全重合,至少应该近似一致。

- 对称性(Symmetry):阵列应同时相对于X轴和Y轴对称。阵列中各单元位置相互对称,而不是单元自身具有对称性。

- 分散性(Dispersion):各个器件的各个分段应尽可能均匀地分布在阵列中。

- 紧凑性(Compactness):阵列的排布尽可能紧凑,尽可能接近正方形。

- 方向性(Orientation):每个匹配器件中应包含等量的朝向相反的段。

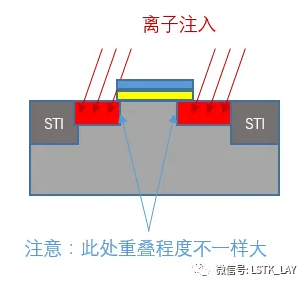

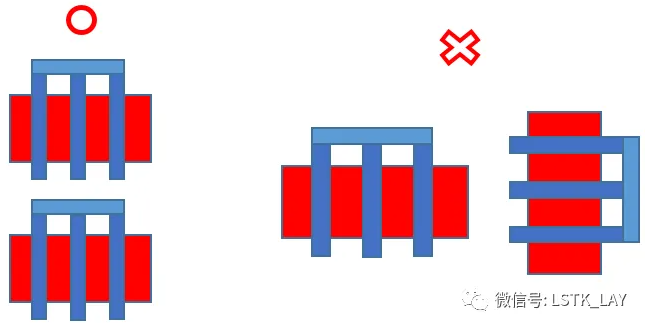

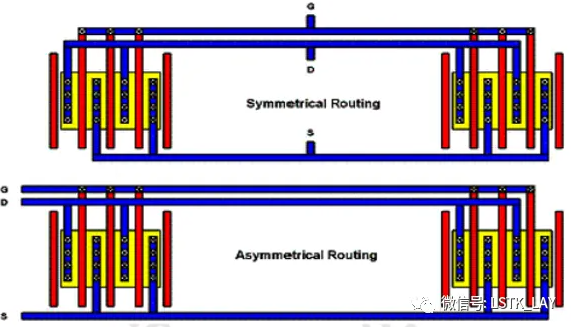

我们知道在离子注入阶段是有一定角度的注入(实际是wafer倾斜一定角度),正因为如此,造成mos管漏源不对称。如下图,所以在mos管的匹配时,应注意保持漏源方向数量的一致性。

举例:

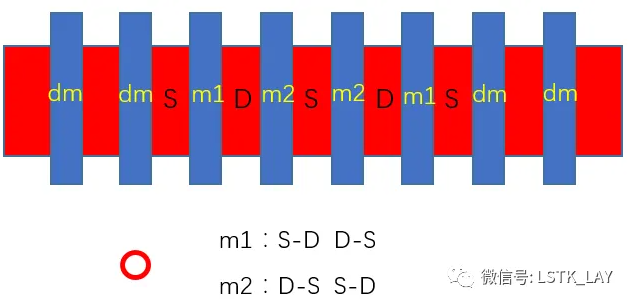

下图满足方向性,m1和m2管分别包含一个S/D和一个D/S,朝向相反且数量相等,故满足方向性要求。

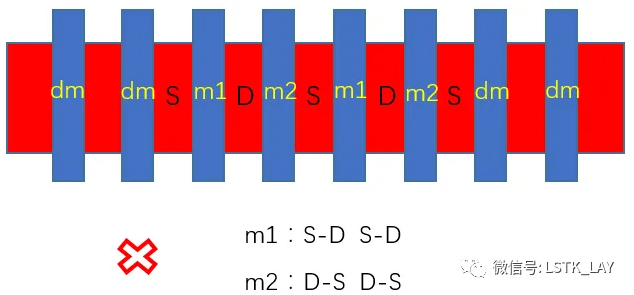

下图不满足方向性,因为m1和m2管中漏源的朝向都是相同的,故不满足方向性要求。

3.3.2 共质心常见的几种方式

注意:共质心布局的复杂度和走线的复杂度成正比(复杂的走线会带来很多的寄生问题),两者需要权衡做出选择。

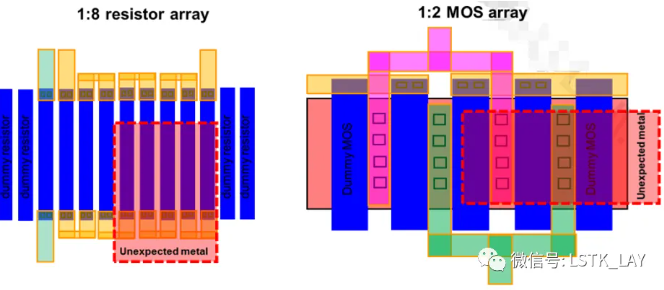

3.4 添加虚拟器件(Dummy devices)

- 增加虚拟器件可以使器件本体避免过度刻蚀(Over Etching)。

- 不管是mos管还是其他器件,增加的虚拟器件和被保护的器件间距需要保证一致。

- 增加的虚拟器件需要连接到衬底,防止引入额外噪声。

4. 匹配中一些注意事项

4.1 保持器件方向一致

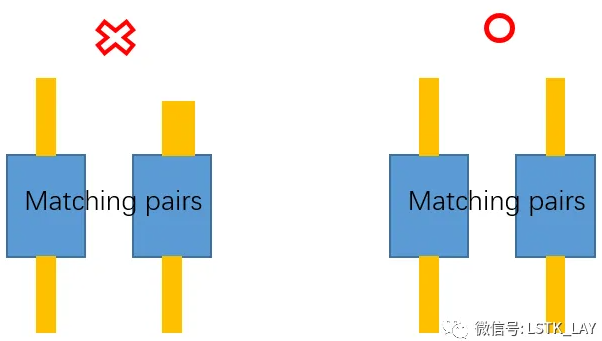

4.2 避免金属走线穿过匹配器件

4.3 对称走线,使走线产生的寄生相同

4.4 放置器件在低应力梯度区域

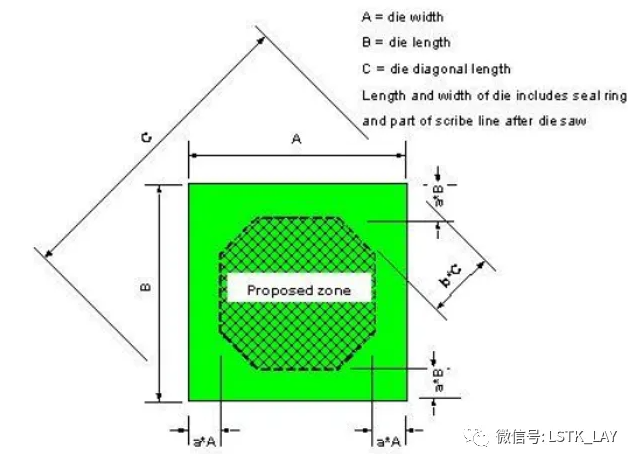

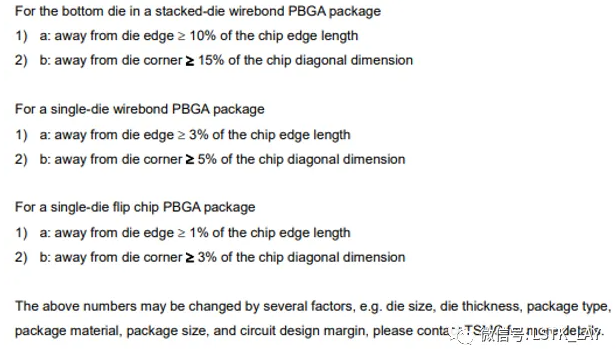

我们知道封装产生的应力是不可避免的,同样不同类型的封装产生的应力对die产生的应力也会有不同。我们在放置关键器件时,应避免高应力区域。

如下是,T家规格书给出的参考。(仅供参考)

4.5 放置器件尽可能远离功率器件

4.6 匹配的器件版图尽可能紧凑

4.7 采用较大尺寸的器件来匹配

4.8 注意制造中二级效应对匹配的影响(点击蓝色字体查看)

5. 问题与讨论

5.1 有没有什么手段可以在tapout前就能看到相关的器件失配呢?

Ans:可以,使用蒙特卡洛(Monte Carlo)仿真看器件的随机失配大小,但不能看到系统失配的大小。

5.2 为什么厚的gate oxide 比薄的gate oxide 的匹配效果差?

Ans:因为厚度gate oxide 是通过多次生产薄的oxide累计上去的。

5.3 能解释下匹配中的绝对精度和相对精度吗?

Ans:匹配不关心绝对精度,只关心相对精度;绝对精度取决于晶圆厂,不同厂商会有微小差异(差别不会太大);相对精度可以通过相关匹配手段来减少。

5.4 共质心匹配是对抗什么类型的误差?

Ans:共质心匹配是对抗系统误差中的梯度效应,和随机误差没有关系。

-END-

参考资料:

- The Art of Analog Layout ,Second Edition——Alan Hastings.

- https://www.youtube.com/watchv=3hxtMYNFsF8&list=PLGEMCz0M6AJ780paAnxP5TqMTpvNs100G&index=7

- tsmc 45/40 nm cmos logic and ms_rf design rule.