本文始于2025年3月,在完成《Abstract 提取LEF文件流程介绍》文章后,发现理解其LEF文件中各语句的具体含义将更加有利于Abstract软件的使用和抽取,两者相辅相成。于是开始撰写本文,旨在让读者会抽取LEF文件的同时还能懂其内各语句的含义,做到知其然,并知其所以然。

值得提及的是:文中内容有借AI协助,但部分词语和内容笔者依旧有增加删减修改,以适应更好的阅读和理解。对本文有疑问的地方,请以help原文为准。如果您对此感兴趣,请继续阅读本文。

2.1 VERSION

2.2 BUSBITCHARS

2.3 DIVIDERCHAR

2.4 UNITS

2.6 USEMINSPACING

2.7 CLEARANCEMEASURE

2.9 FIXEDMASK

2.10 LAYER

2.11 MAXVIASTACK

2.12 Via\Via Rule\Via Rule Generate

2.13 NONDEFAULTRULE

2.14 SITE

2.15 EXTENSIONS

3. Cell Library LEF(IP LEF)中的格式及语法说明

3.1 CLASS

3.2 FOREIGN

3.3 ORIGIN

3.4 SIZE

3.5 SYMMETRY

3.6 PIN

3.7 OBSTRUCTION

4. 参考

1. 什么是LEF文件,LEF文件有啥作用?

LEF是Library Exchange Format 的缩写,它包含两个部分,分别是:Technology LEF 和 Cell Library LEF (IP LEF)。这两个部分可以放在一个LEF文件中,但由于放在一个文件中相对来说,会比较多比较复杂,不易查看和阅读。所以通常会将拆分为两个LEF文件,也就是上面说的两个部分。都是文本文件,支持手动修改。

其中:

Technology LEF文件:描述了工艺相关的规则信息,如层定义、通孔大小、间距要求、线宽约束、布线层数等工艺参数。

Cell Library LEF (IP LEF)文件:描述了cell或IP的物理特性,如cell或IP的几何形状、引脚位置信息、使用的金属层数等,它是抽象的,是一个简化后的版图。此部分的LEF文件主要通过Abstract软件抽取获得。

应用场景:

LEF 文件通常用于布局布线工具(如 Cadence Innovus、Synopsys IC Compiler)初始化芯片的物理设计规则和单元库数据。为后续PR做好准备。

2. Technology LEF格式及语法说明

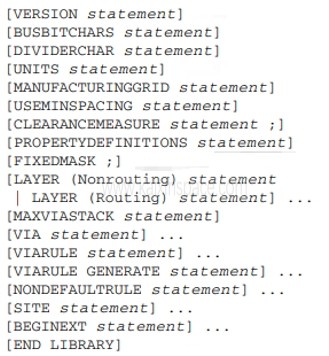

通常一个标准的Technology LEF文件具有以下格式:

下面介绍各个字段的意义:

2.1 VERSION

语法:VERSION version_number;

示例:

VERSION 5.7 ###表示LEF文件使用的版本是5.72.2 BUSBITCHARS

语法:BUSBITCHARS "delimiter_pair";

示例:

BUSBITCHARS "[]"; ###定义bus标志符号,端口名称含有"[]",将被看成bus2.3 DIVIDERCHAR

语法:DIVIDERCHAR "character";

示例:

DIVIDERCHAR "/"; ###表示LEF中将使用"/"分割层次的字符2.4 UNITS

UNITS 语句用于定义所有度量单位,使设计工具能够正确解释LEF文件中使用的数值。该语句指定了不同物理量(如时间、电流、电压等)的单位,并为这些单位提供转换因子。这些转换因子确保LEF文件中的单位能够正确映射到设计工具所使用的数据库单位(DBUs)中。

UNITS 语法示例:

UNITS

TIME NANOSECONDS convertFactor ;

CAPACITANCE PICOFARADS convertFactor ;

CURRENT MILLIAMPS convertFactor ;

DATABASE MICRONS LEFconvertFactor ;

FREQUENCY MEGAHERTZ convertFactor ;

END UNITS ;参数说明:

- TIME NANOSECONDS convertFactor:将LEF中的时间单位解释为纳秒(NANOSECONDS),并提供转换因子,将其转换为数据库单位(DBUs)。

- CAPACITANCE PICOFARADS convertFactor:将LEF中的电容单位解释为皮法拉(PICOFARADS),并提供转换因子。

- CURRENT MILLIAMPS convertFactor:将LEF中的电流单位解释为毫安(MILLIAMPS),并提供转换因子。

- DATABASE MICRONS LEFconvertFactor:定义LEF中的距离单位(微米,MICRONS)转换为数据库单位的转换因子。如果省略该语句,默认值为100,表示1微米等于100个数据库单位(DBUs)。

- FREQUENCY MEGAHERTZ convertFactor:将LEF中的频率单位解释为兆赫兹(MEGAHERTZ),并提供转换因子。

UNITS 的意义:

- 单位定义与转换:通过

UNITS语句,LEF文件中的数值可以被转换成工具所需的数据库单位。例如,TIME NANOSECONDS convertFactor会把LEF中的时间单位(纳秒)转换为设计工具中的数据库单位,确保所有物理量在布局中被一致地解析和处理。 - 支持多种物理量:

UNITS语句不仅支持距离(如微米)、时间(如纳秒)、电流(如毫安)、电容(如皮法拉)等常见物理量,还支持频率、功率、电阻等其他重要物理量的定义和转换。这些单位的转换因子确保不同工具或工艺节点间的一致性。 - 数据库单位映射:例如,在

DATABASE MICRONS LEFconvertFactor语句中,LEF中的微米单位(MICRONS)会转换为特定数量的数据库单位(DBUs),例如,1微米可以转换为100数据库单位,确保物理设计的精确度。

UNITS 语句是LEF文件中的一个重要部分,它通过定义单位及其转换因子,确保LEF文件中的数值在不同设计工具和数据库之间的一致性。这使得不同工具可以正确解释并处理LEF文件中的物理数据 。

2.5 MANUFACTURINGGRID

语法:[MANUFACTURINGGRID value] ;

MANUFACTURINGGRID 0.005 ###工艺生产格点2.6 USEMINSPACING

USEMINSPACING语句用于控制如何计算最小间距(spacing)对于障碍(obstruction)几何形状。其主要作用是决定是否将宏(MACRO)的OBS(障碍)形状当作最小宽度的线进行处理,从而影响最小间距的计算。

USEMINSPACING选项

- ON:将障碍(OBS)形状当作最小宽度的线来计算间距。也就是说,宏的OBS形状会被看作是一个最小宽度的线路,所有与其交互的其他元素会基于最小宽度的规则来计算间距。这种模式适用于一些较为简化的设计情况,但可能导致更保守的间距要求,尤其是在一些使用了较大面积的OBS形状时。

- 推荐使用:

ON用于较为旧的设计抽象,尤其是工艺节点在130nm及以下时。但如果使用不当,可能会引发一些DRC错误。

- 推荐使用:

- OFF:将障碍形状作为一个普通的宏来计算间距。这样,在计算间距时不会过于保守,而是更符合实际布局的宽度要求。通常,较宽的OBS形状会使用较宽的线间距规则,而较窄的OBS形状则会使用较窄的线间距规则。

- 推荐使用:

OFF是更优的选择,特别是在更现代的设计中,它更适合大多数工艺节点,避免了一些不必要的保守计算。

- 推荐使用:

示例:

USEMINSPACING OBS OFF ;此语句表示在计算最小间距时,OBS障碍将不被当作最小宽度线来处理,而是按实际宏的宽度来计算间距。

USEMINSPACING 的作用在于如何处理宏的OBS形状对间距计算的影响,ON时会导致较为保守的计算,而OFF则提供较为实际的计算方法。

2.7 CLEARANCEMEASURE

CLEARANCEMEASURE 语句在LEF文件中的作用是指定计算所有物体间距(如在 SPACING 和 SPACINGTABLE 语句中使用的间距)时应使用的间距度量方法。具体而言,它定义了距离计算的规则,选择两种不同的计算方式:MAXXY 和 EUCLIDEAN。

语法:

CLEARANCEMEASURE {MAXXY | EUCLIDEAN} ;含义:

- MAXXY:使用物体在x轴和y轴方向的最大距离来计算间距。这意味着计算间距时,只有在x和y方向上最远的点会被考虑,适用于需要考虑最大方向距离的设计。

- EUCLIDEAN:使用欧几里得距离,即计算两点之间的直线距离。此方法计算物体间的实际空间距离,通常适用于大多数设计情况。

默认值:

如果没有明确指定 CLEARANCEMEASURE,则默认使用 EUCLIDEAN 计算方式。

优缺点:

- MAXXY(最大XY):

- 优点:适用于某些设计规则,例如要求在x轴和y轴上都保持一定的最小间距时,可以确保设计的最大间距符合要求。

- 缺点:可能会导致计算的间距比实际的直线距离要大,从而浪费更多空间。

- EUCLIDEAN(欧几里得):

- 优点:计算的是实际的直线距离,能够提供更精确的设计空间计算,尤其适用于复杂的布局和密集的设计。

- 缺点:在某些情况下,如果设计规则要求最大方向间距而非直线间距,使用欧几里得计算可能不够保守。

示例:

CLEARANCEMEASURE MAXXY ;这表示在计算间距时使用最大XY距离,即在x和y方向上最大的距离。

CLEARANCEMEASURE EUCLIDEAN ;这表示使用欧几里得距离来计算物体之间的最短直线距离。

2.8 PROPERTYDEFINITIONS

PROPERTYDEFINITIONS 语句用于定义设计中的所有属性。这些属性可以应用于不同的设计元素,如库、宏、PIN、VIA、VIARULE等。通过定义属性,用户可以指定这些元素的特定行为、约束和特性。

PROPERTYDEFINITIONS 的语法:

PROPERTYDEFINITIONS

[objectType propName propType [RANGE min max] [value | "stringValue"];

END PROPERTYDEFINITIONS参数说明:

- objectType:指定属性应用的对象类型。可以是以下之一:

LAYER:层的属性LIBRARY:库的属性MACRO:宏的属性PIN:引脚的属性VIA:通孔的属性VIARULE:通孔规则的属性INTEGER、REAL、STRING:其他数据类型

- propName:属性的名称。每个对象类型都可以有一个或多个属性。

- propType:属性的类型,可以是

INTEGER、REAL或STRING等。 - RANGE min max:对于数值型属性,可以指定一个范围,限制属性的有效值。

- value 或 stringValue:属性的具体值,可以是数字或字符串。

定义示例:

示例1:定义库属性

PROPERTYDEFINITIONS

LIBRARY versionNum INTEGER 12;

LIBRARY title STRING "Cadence96";

END PROPERTYDEFINITIONS这段代码定义了库的两个属性:

versionNum:一个整数类型的属性,值为12。title:一个字符串类型的属性,值为 “Cadence96″。

示例2:定义宏属性

PROPERTYDEFINITIONS

MACRO weight REAL RANGE 1.0 100.0;

MACRO type STRING;

END PROPERTYDEFINITIONS这段代码定义了两个宏的属性:

weight:一个实数类型的属性,范围在1.0到100.0之间。type:一个字符串类型的属性,通常用于表示宏的类别或类型。

应用场景:

- 宏属性:如在LEF文件中,宏(

MACRO)可以有诸如weight、type等属性,这些属性可以影响布局、布线或功能的行为。 - 引脚属性:通过

PROPERTY可以为引脚定义特殊行为,如时钟引脚、复位引脚等。 - 层属性:通过为每个层定义属性,可以进一步描述该层的制造规则或特性,例如层的宽度、间距等。

PROPERTYDEFINITIONS 用于集中定义设计中各种对象的属性。通过在LEF文件中明确这些属性,设计者能够在设计的每个阶段引用并管理它们,确保设计的正确性和一致性。这些属性在设计规则检查(DRC)、布局优化等方面起着至关重要的作用。

2.9 FIXEDMASK

FIXEDMASK语句的作用是禁止掩膜移动,确保宏单元的引脚掩膜分配保持固定,不能为了优化布线密度而将其移到不同的掩膜层。这对于一些采用多掩膜工艺的技术非常重要,尤其是在设计中使用多掩膜层来优化布线和掩膜分配时。

FIXEDMASK 的意义:

- 不允许掩膜移动:当在LEF文件中使用

FIXEDMASK时,所有宏引脚的掩膜分配必须保持固定。即使在布局优化过程中,掩膜也不能为了提高布线密度而进行调整或重新分配。这对于要求高度精确的制造工艺(如双重或三重掩膜工艺)非常关键。 - 适用的场景:一些技术在使用多掩膜层时,要求引脚和路由形状的掩膜不能改变。比如,针对某些特殊工艺,掩膜的颜色可能已预先定义,并且必须严格遵循,因此不允许改变掩膜的分配。

语法示例:

FIXEDMASK ;该语句通常在LAYER语句之前出现,表示接下来定义的宏单元引脚掩膜不允许变动。

应用场景:

- 多掩膜工艺:对于使用多掩膜的设计技术,

FIXEDMASK确保引脚和路由的掩膜不被改变,这对于满足制造工艺要求至关重要。 - 固定掩膜分配:在一些高精度的设计中,某些区域(如引脚)必须使用特定的掩膜,

FIXEDMASK帮助保持这些掩膜分配的一致性。

FIXEDMASK用于确保LEF文件中所有宏引脚的掩膜分配保持固定,特别适用于多掩膜工艺或需要严格掩膜管理的技术,以确保设计的可制造性和符合工艺要求 。

2.10 LAYER

Layer (Cut)、Layer (Implant)、Layer (Masterslice or Overlap)、Layer (Routing) 等层类型定义了不同的工艺层,每种层的功能和应用场景有所不同,下面分别解释它们的意义。

2.10.1 Layer (Cut)

- 定义:

CUT层用于表示切割层,它通常用于定义VIA或接触的区域,主要用于通孔(via)的定义。 - 功能:

CUT层在布线过程中通常用于连接不同的金属层。CUT层由通孔规则(VIARULE)定义,它在整个设计中至关重要,尤其是在多层集成电路的互连过程中。

LAYER VIA1

TYPE CUT;

END VIA1这段代码定义了一个名为 VIA1 的切割层。

2.10.2 Layer (Implant)

- 定义:

IMPLANT层定义了半导体中掺杂的区域,如高驱动或低驱动的掺杂层。它们对电流传输和驱动能力有直接影响。 - 功能:

IMPLANT层规定了掺杂区域的最小宽度、最小间距等规则,通常用于规定芯片中各个单元的位置约束。

LAYER implant1

TYPE IMPLANT;

WIDTH 0.50;

SPACING 0.50;

END implant1这段代码定义了一个掺杂层 implant1,并指定了最小宽度和最小间距。

2.10.3 Layer (Masterslice or Overlap)

- 定义:

MASTERSLICE层和OVERLAP层用于定义一些特殊的非路由层和重叠层。MASTERSLICE通常用于固定的层,OVERLAP用于宏单元中的矩形块和检查。 - 功能:

- MASTERSLICE:主要用于描述固定的多晶硅层,通常需要通过VIA连接。它不允许进行布线,只作为连接的通道。

- OVERLAP:用于检查和描述宏单元重叠区域的障碍物,用于形成形状规则的单元或块。

LAYER poly

TYPE MASTERSLICE;

END poly

LAYER overlap

TYPE OVERLAP;

END overlap这段代码定义了一个多晶硅层 poly 和一个重叠层 overlap。

2.10.4 Layer (Routing)

- 定义:

ROUTING层用于路由层,实际的布线会发生在这些层上。它们包含不同的金属层,如metal1、metal2等,用于连接芯片中的各个元件。 - 功能:

ROUTING层是设计中的核心层,用于定义不同层之间的电连接。每个路由层可以有不同的间距、宽度、方向等约束。

LAYER metal1

TYPE ROUTING;

WIDTH 0.23;

SPACING 0.23;

DIRECTION HORIZONTAL;

END metal1这段代码定义了一个水平的 metal1 路由层,指定了宽度和间距。

总结:

- CUT 层:用于定义通孔,连接金属层。

- IMPLANT 层:定义掺杂区域的层,控制电流传输。

- MASTERSLICE/OVERLAP 层:用于定义特定的非路由层,如多晶硅层和重叠层。

- ROUTING 层:用于定义实际的布线层,连接各个元件。

这些层的定义确保了芯片设计中各个功能区域的正确实现,并符合制造工艺要求 。

2.11 MAXVIASTACK

MAXVIASTACK 语句的意义:

MAXVIASTACK 用于定义允许的单切通孔堆叠的最大数量。堆叠via 是指多个通孔(via)叠加在一起,通常用于连接不同的金属层。在某些设计规则中,需要对通孔堆叠的高度进行限制,以避免影响制造和性能。

语法:

MAXVIASTACK value [RANGE bottomLayer topLayer] ;参数说明:

- value:指定允许的最大单切通孔堆叠数量。

value是一个整数,表示堆叠的通孔数量。例如,MAXVIASTACK 4;表示允许最多堆叠 4 层单切通孔。 - RANGE bottomLayer topLayer:可选参数,指定适用的层范围。如果未指定,默认该规则适用于所有层。此参数用于限定堆叠规则仅适用于某些金属层之间的堆叠,如

MAXVIASTACK 4 RANGE metal1 metal7;表示最大堆叠限制适用于从metal1到metal7的金属层。

功能与应用:

- 控制通孔堆叠:

MAXVIASTACK控制的是每个通孔堆叠的高度,确保通孔堆叠的数量不超过设计规定的最大值。堆叠过多的通孔可能导致布线密度过高,或影响制造工艺,因此设置此规则有助于确保设计的可制造性和性能。 - 堆叠的定义:通过堆叠定义的通孔数是基于切割层(cut layer)。如果多个via的切割部分重叠,则这些via被认为是堆叠的。堆叠的数量受到

MAXVIASTACK规则的限制。例如,如果堆叠中有一个双切(double-cut)via,它会打断堆叠,使得堆叠层数减少。

示例:

MAXVIASTACK 4 ;此语句表示在整个设计中,单切通孔的堆叠最多允许4层。

如果限定特定的层范围:

MAXVIASTACK 4 RANGE metal1 metal7 ;此语句表示在 metal1 到 metal7 层之间,最多只能堆叠 4 层通孔。

MAXVIASTACK 限制了设计中允许的最大堆叠通孔数量,确保设计不会因堆叠过多的通孔而导致制造难度增加或性能问题。通过设置堆叠的最大值,设计师能够更好地控制布局密度、制造工艺和信号完整性 。

2.12 Via\Via Rule\Via Rule Generate

2.12.1 Via

- 定义:

VIA定义了通孔(via),用于连接芯片中不同金属层之间的电路。每个 via 包含三个层:两个金属层(或主切片层)以及一个用于切割的层。 - 类型:

- 固定 via:使用矩形或多边形定义,并且不依赖

VIARULE。其名称必须在所有相关的 LEF 和 DEF 文件中保持一致。 - 生成 via:使用

VIARULE参数定义,表示该 via 是由VIARULE GENERATE语句生成的。

- 固定 via:使用矩形或多边形定义,并且不依赖

2.12.2 VIARULE

VIARULE 语句用于描述通过特定规则生成的通孔。它规定了如何选择和生成合适的通孔,包括:

- 层(LAYER):指定上层和下层金属层,通常包括一个切割层。

- 方向(DIRECTION):定义布线方向(水平或垂直),以决定何时应用该规则。

- 宽度(WIDTH):可以指定最小和最大宽度,用于限定符合条件的布线。

- VIA:列出适合在此规则下使用的通孔,如果这些通孔可以在给定位置上放置而不违反设计规则,便会被选用。

- 属性(PROPERTY):可以定义附加的属性,例如电阻等。

示例:

VIARULE viaRule1

LAYER metal1 ;

DIRECTION HORIZONTAL ;

WIDTH 0.5 TO 1.0 ;

LAYER metal2 ;

DIRECTION VERTICAL ;

WIDTH 1.0 TO 2.0 ;

VIA via12_1 ;

VIA via12_2 ;

END viaRule1在这个示例中,viaRule1 定义了一个通孔规则,它规定在水平金属层 metal1 和垂直金属层 metal2 之间使用的通孔 via12_1 或 via12_2,当它们的宽度在指定范围内时,将会被选用。

2.12.3 VIARULE GENERATE

- 定义:

VIARULE GENERATE用于自动生成 via,通常用于特殊的布线场景。它通过设置层、封闭区域、宽度范围等参数来定义如何生成 vias,而不是手动列出每个具体的 via。 - 应用场景:

- 自动生成 via:使用

VIARULE GENERATE可以通过给定的规则和条件自动生成符合设计要求的 vias。这种方法适用于不常见的布局情况,避免手动逐一定义所有 vias 。

- 自动生成 via:使用

- LAYER:定义上层、下层和切割层。

- ENCLOSURE:定义金属层的覆盖距离,确保金属层充分覆盖通孔。

- CUTSIZE:指定切割层的大小。

- SPACING:定义切割层的间距,通常是中心到中心的间距。

- RESISTANCE:指定通孔的电阻。

示例:

VIARULE viaRule1 GENERATE DEFAULT

LAYER metal1 ;

ENCLOSURE 0.03 0.01 ;

LAYER metal2 ;

ENCLOSURE 0.05 0.01 ;

LAYER cutLayer ;

RECT -0.1 -0.1 0.1 0.1 ;

SPACING 0.40 BY 0.40 ;

RESISTANCE 20 ;

END viaRule12.13 NONDEFAULTRULE

NONDEFAULTRULE 是定义非默认路由规则的语句。它允许为特定的信号网或宏单元设置与默认规则不同的布局规则。这些规则包括层宽、间距、使用的通孔以及与特定层组合的规则。

NONDEFAULTRULE 的作用和意义:

- 定义非默认规则:

NONDEFAULTRULE用于定义与默认路由规则不同的布局约束,如特定层的最小宽度、间距等,或者指定特殊的通孔规则。 - 为每个网络指定规则:如果你需要针对特定网络(比如时钟网、信号网)使用不同的设计规则,可以通过

NONDEFAULTRULE来定义专用规则。 - 可以指定多个规则:你可以定义多个

NONDEFAULTRULE,为不同的层和设计元素设置不同的宽度、间距和其他约束。

语法结构:

NONDEFAULTRULE ruleName

LAYER layerName

WIDTH width

SPACING spacing

VIA viaName

END layerName

...

END ruleName示例:

假设你想为某些信号网定义较宽的金属层和较大的间距规则,可以使用如下定义:

NONDEFAULTRULE wideSpacingRule

LAYER metal1

WIDTH 1.5

SPACING 0.5

END metal1

LAYER metal2

WIDTH 1.5

SPACING 0.5

END metal2

END wideSpacingRule在这个例子中,wideSpacingRule 定义了两个层(metal1 和 metal2)的最小宽度为1.5μm,间距为0.5μm。

非默认规则的用途:

- 增加电流承载能力:如果需要更宽的线路或更大间距来增加电流承载能力或降低信号串扰,可以使用

NONDEFAULTRULE来指定这些特性。 - 避免制造问题:通过精确控制规则(如通孔的数量或层间距),避免在制造过程中出现问题。

- 支持多层工艺:对于多层工艺和复杂的芯片布局,

NONDEFAULTRULE可以定义一些特殊的设计约束,如金属层之间的最小距离、不同的通孔类型等。

NONDEFAULTRULE 使得设计者能够定义与默认规则不同的自定义设计规则,适用于特定的设计需求,如电流、信号完整性、制造容差等。它通过提供更多灵活性,确保设计可以满足特定的工艺和功能要求。

2.14 SITE

SITE 语句用于定义设计中的放置位置(site),这些位置为宏单元的布局提供了网格。在设计过程中,SITE 是非常重要,它为设计中宏的布局提供了约束。不同类型的SITE定义可以决定宏在设计中的放置模式,比如在核心区域的标准单元、输入/输出引脚区域等。

SITE 语法:

SITE siteName

CLASS {PAD | CORE} ;

[SYMMETRY {X | Y | R90} ... ;]

[ROWPATTERN {previousSiteName siteOrient} ... ;]

SIZE width BY height ;

END siteName参数说明:

siteName:指定该位置的名称,通常是自定义的标识符,用于标识该放置位置。CLASS:定义该位置的类别,可以是PAD(输入/输出引脚)或CORE(用于核心区域的单元放置)。SYMMETRY:定义该位置的对称性。常见的对称性包括X(沿X轴对称)、Y(沿Y轴对称)、R90(旋转90度对称)等,用于指导宏的对称布局。ROWPATTERN:定义一个站点模式,可以通过该模式在布局中创建一系列连续、规则的站点,通常是多个站点在某个方向上的重复排列。SIZE width BY height:定义该站点的尺寸,单位通常是微米。

应用场景:

- 输入/输出区域 (

PAD):SITE PAD用于指定输入/输出区域的站点,在这些站点上放置宏用于I/O连接。 - 核心区域 (

CORE):SITE CORE用于指定核心区域的放置位置,在这些区域内放置核心逻辑单元。

示例:

1. 标准单元站点:

SITE Fsite

CLASS CORE ;

SIZE 4.0 BY 7.0 ;

END Fsite这段代码定义了一个名为 Fsite 的站点,表示一个核心区域的标准单元,宽度为4.0微米,高度为7.0微米。

2. 多站点模式:

SITE mySite

ROWPATTERN Fsite N Lsite N Lsite FS ;

SIZE 16.0 BY 7.0 ;

END mySite这段代码定义了一个站点模式 mySite,它由多个 Fsite 和 Lsite 站点组成,并且指定了站点的排列模式(例如,N、FS 表示不同的站点方向)

SITE 语句在LEF文件中用于定义设计中站点的位置和布局规则。这些站点为宏单元提供了一个固定的放置网格,使得设计能够高效地进行布局规划。通过 SYMMETRY 和 ROWPATTERN 等设置,可以进一步控制站点的对称性和排列方式,确保在设计中的位置和约束条件的合理性 。

2.15 EXTENSIONS

EXTENSIONS 语句用于向文件添加自定义的语法扩展。这些扩展可以由不支持该语法的工具忽略,也可以用于在LEF/DEF文件中增加新的功能或数据格式。EXTENSIONS语句通常用于添加不被当前版本的LEF/DEF文件支持的语法,尤其是在版本5.1及以后。

EXTENSIONS 语法:

[BEGINEXT "tag"

extensionText

ENDEXT]- “tag”:标识扩展块的标签,必须用引号括起来。标签通常用于标识该扩展的类型或用途。

- extensionText:定义扩展的内容。工具会忽略这些内容,如果它们不被支持,但可以被某些特定工具或系统所解析。

功能与应用:

- 自定义语法:用户可以通过

EXTENSIONS语句自定义LEF/DEF文件的内容,添加工具或工艺特定的参数。这样,文件就能够包含特定工具或需求的附加信息。 - 扩展工具支持:当使用较新版本的LEF/DEF格式,或者需要与老旧版本兼容时,

EXTENSIONS为用户提供了在文件中插入不被当前工具支持的新语法的方式。 - 向后兼容:

EXTENSIONS语句使得LEF文件能够扩展新的功能,同时确保较老的工具可以忽略这些扩展而不影响设计的正确性。

示例:

BEGINEXT "1VSI Signature 1.0"

CREATOR "company name"

DATE "timestamp"

REVISION "revision number"

ENDEXT这个示例向LEF文件中添加了一个名为"1VSI Signature 1.0"的扩展,包含创建者、日期和版本号等信息。

EXTENSIONS语句用于在LEF文件中加入自定义扩展内容,可以添加新的语法或工具特定的属性。它确保文件可以灵活扩展,同时保持与旧版工具的兼容性】。

3. Cell Library LEF(IP LEF)中的格式及语法说明

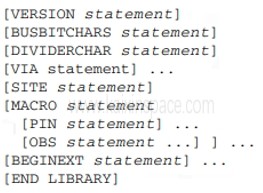

通常一个标准的Cell Library LEF(IP LEF)LEF文件具有以下格式:

这里将介绍”MACRO”中的一些关键词定义,而涉及到其他的关键字,请参考上述Technology LEF中的介绍。

3.1 CLASS

CLASS 是用来指定宏单元的类型。它定义了宏的用途、功能和布置方式。以下是分别介绍不同类型的CLASS及其意义:

3.1.1 COVER

- 定义:表示一个固定布局的宏,不能更改,通常用于电源环绕核心的布线。

- 子类:

- BUMP:仅包含顶层“bump”金属层的物理单元。

BUMP层通常用于封装技术,定义物理连接的金属凸点。

- BUMP:仅包含顶层“bump”金属层的物理单元。

3.1.2 RING

- 定义:大型宏,具有内部电源网格,仅在宏的边界上暴露电源引脚。这种宏通常用于电源域内的电源切换单元,或用于构建电源环。

- 应用:常用于电源或电源开关单元的封装,以便在电源环内提供连接。

3.1.3 BLOCK

- 定义:预定义的宏,用于层次化设计。它们可以被进一步细分为以下子类:

- BLACKBOX:一个占用总面积的预定义宏,通常没有详细的实现,只提供一个大致的尺寸估计。它也可能包含引脚,但很多情况下,宏引脚名通过Verilog描述获取,而无需与LEF中的引脚名匹配。

- SOFT:一个不完全实现的宏单元,其子模块可能仍然处于可修改状态,允许部分修改(例如宽度、引脚位置等)。

3.1.4 PAD

- 定义:用于I/O连接的引脚宏,可以是:

- INPUT、OUTPUT、INOUT、POWER、SPACER、AREAIO(用于没有内建凸点的区域I/O驱动单元)等类型。

- 应用:用于I/O区域与芯片外部连接,或者用于区域内驱动连接。

3.1.5 CORE

- 定义:用于核心区域的标准单元宏。通常应包含一个

SITE定义,以便标准单元布线工具可以正确对齐核心宏到标准单元行。 - 子类:

- FEEDTHRU:用于连接其他单元的核心单元。

- TIEHIGH/TIELOW:用于连接未使用的I/O终端到电源或地线总线。

- SPACER:用于填充标准单元行之间的空隙,通常没有逻辑引脚,仅包含电源和接地引脚。

- ANTENNACELL:用于解决工艺中的天线效应问题。

- WELLTAP:用于将N型和P型扩散井连接到正确的电源或地线。

3.1.6 ENDCAP

- 定义:用于封装核心行端点的宏,用于连接电源布线。可以是:

- PRE、POST:分别位于核心行的左端或右端。

- TOPLEFT、TOPRIGHT、BOTTOMLEFT、BOTTOMRIGHT:分别位于四个角的位置,用于I/O端口。

CLASS 语句用于指定宏的类型,每种类型对应不同的功能和布置规则。例如,COVER宏通常用于固定布局和电源环,BLOCK宏用于层次化设计,PAD宏用于I/O连接等。通过设置不同的CLASS,设计者可以清晰地定义每个宏单元的作用和约束 。

3.2 FOREIGN

FOREIGN 语句用于定义一个外部的(通常是GDSII格式的)结构,用于表示一个宏的布局实例。它表明在实际布局中使用了外部的单元或组件,并可以选择性地提供偏移量和方向,确保在整个布局中正确放置该宏。

FOREIGN 语法:

FOREIGN foreignCellName [pt [orient]];- foreignCellName:表示外部结构(如GDSII文件中的单元)名称。

- pt(可选):指定宏的原点偏移量。如果pt没有指定,默认情况下,pt坐标是(0 0)。

- orient(可选):指定宏的方向,默认方向为北向(N)。其他方向包括南(S)、东(E)、西(W)、翻转90度(R90)等。

示例:

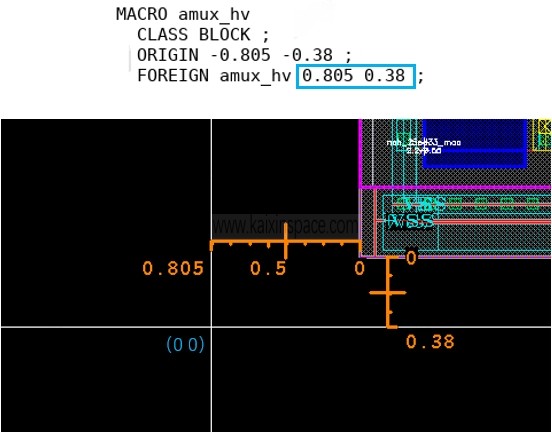

MACRO amux_hv

FOREIGN amux_hv 0.805 0.38 ;

END amux_hv以上示例表示在布局中使用名为 amux_hv 的外部单元,该单元的位置相对于坐标原点偏移(0.805 0.38),如下图;

3.3 ORIGIN

ORIGIN 语句用于定义宏的原点(或称为“基准点”),它决定了宏在设计中如何对齐。具体来说,ORIGIN 语句指定了一个坐标点,表示宏的几何形状在与其他宏组件布局对齐时的偏移量。这个偏移量会影响宏的实际放置位置。

ORIGIN 语法及功能:

ORIGIN pt ;- pt:表示坐标点,通常是以微米为单位的x和y坐标。

- 如果没有提供

ORIGIN语句,该组件布局会默认与宏的北向(NORTH)方向的 (0, 0) 对齐。 - 如果提供了

ORIGIN语句,则宏的位置会先按指定的ORIGIN偏移。

举例说明:

假设在宏定义中使用以下 ORIGIN 语句:

ORIGIN 0 -1 ;这意味着:宏的位置最初会被调整到 (0, -1) 位置,这里注意与宏本身FOREIGN 坐标的关系。然后,它会根据PR软件中指定的位置放置,这样宏的实际放置位置会受到偏移的影响。

举例:ORIGIN 与 FOREIGN坐标之间的关系

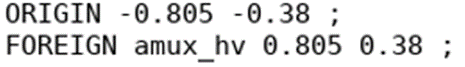

当在LEF文件中指定坐标:ORIGIN 为(-a -b),而指定坐标:FOREIGN 为(-c -d)时,此时当你将LEF导入到相关后端软件后,其导入的宏组件坐标的位置将是:(-c+(-a)) (-d+(-b))。

然而幸运的是,在Abstract抽取版图LEF文件时,即使你抽取的版图相对于原点有偏移(FOREIGN),在导出LEF文件后,ORIGIN关键字也会自动帮助您修复偏移的位置,使得你在导入该版图的LEF文件到后端软件中坐标都是在原点位置。即,ORIGIN的坐标始终和您抽取LEF的坐标相反。如下;

ORIGIN a b

FOREIGN -a -b

3.4 SIZE

SIZE语句用于定义宏的尺寸,即宏的边界矩形。这个矩形从原点 (0, 0) 扩展到由 SIZE 语句指定的 width 和 height,并表示宏在设计中的面积。它帮助工具计算和管理宏在布局中的位置。

SIZE 语法

SIZE width BY height ;含义:

width:表示宏的宽度,单位为微米(microns)。height:表示宏的高度,单位为微米(microns)。

该语句定义的宏边界矩形通常用于布局工具进行宏的定位和放置。设计工具将使用这个边界矩形来决定宏的实际布局位置和与其他宏的相对位置。

功能和应用:

- 定义宏的面积:

SIZE语句帮助定义宏的外部尺寸,通常用于设计中宏的布局和排布。 - 防止重叠:

SIZE语句提供的边界矩形帮助工具避免宏之间的重叠,除非使用OBS OVERLAP来定义可重叠区域。 - 布局工具使用:布局工具通常使用

SIZE来决定宏的放置位置,并根据该矩形与其他宏的矩形进行比较,确保它们不重叠。

示例:

SIZE 10.0 BY 40.0 ;这表示宏的宽度为 10.0 微米,高度为 40.0 微米,布局工具将使用该边界矩形来安排宏的位置。

SIZE 语句在LEF文件中定义了宏的尺寸,表示宏的外部边界矩形。它对布局工具的宏放置至关重要,确保宏在设计中正确放置,并且避免与其他宏重叠。

3.5 SYMMETRY

SYMMETRY {X | Y | R90} 是用于描述宏的对称性及其合法旋转和翻转方式的语法。它指示在布局时,如何允许宏旋转或翻转,以便与其所在的站点(site)匹配。

SYMMETRY 的含义和分类:

- X 对称(

SYMMETRY X):- 描述:宏在 X 轴上对称。也就是说,当宏围绕 X 轴翻转时,它将与原始位置对称匹配。

- 可能的方向:如果指定

SYMMETRY X,则宏可以匹配N(北)和FS(翻转南)方向的站点。

- Y 对称(

SYMMETRY Y):- 描述:宏在 Y 轴上对称。即,宏围绕 Y 轴翻转时,它将与原始位置对称匹配。

- 可能的方向:指定

SYMMETRY Y时,宏可以匹配N(北)和FN(翻转北)方向的站点。

- XY 对称(

SYMMETRY X Y):- 描述:宏在 X 轴和 Y 轴上都对称。即,宏可以进行 X 轴和 Y 轴的翻转,从而与其原始位置对称匹配。

- 可能的方向:

SYMMETRY X Y允许宏匹配四个方向:N(北),FN(翻转北),FS(翻转南),和S(南)。

- 90° 旋转(

SYMMETRY R90):- 描述:宏的 90 度旋转。通常用于非标准单元,指示宏应该尝试通过 90 度的旋转来匹配站点。

- 适用场景:

R90主要用于一些需要特定旋转的宏,在标准单元中不常用。

用途和示例:

SYMMETRY 语句告诉布局工具,在设计中安排宏时,可以接受哪些旋转或翻转的方向。例如,对于一个标准单元宏,通常希望它具有 SYMMETRY X Y,以便能够适应多种站点的布局方向。

示例1:

SYMMETRY X Y ;这表示宏支持在 X 和 Y 轴上的对称性,可以匹配四个方向:N,FN,FS,和 S。

示例2:

SYMMETRY X ;这表示宏仅支持 X 轴上的对称性,可以匹配 N 和 FS 方向的站点。

- SYMMETRY X:在 X 轴上对称,支持

N和FS方向。 - SYMMETRY Y:在 Y 轴上对称,支持

N和FN方向。 - SYMMETRY X Y:在 X 和 Y 轴上都对称,支持

N,FN,FS,S四个方向。 - SYMMETRY R90:指定宏的 90 度旋转,适用于非标准单元。

这些对称性设置帮助确定宏在布局时如何被放置,并确保宏能够适应不同的站点布局和方向。

3.6 PIN

Pin Statement 用于定义宏中的引脚及其相关属性。引脚是宏与外部电路进行连接的接口。每个引脚都需要在宏的布局中定义,通常会指定引脚的方向、位置、层次、以及其他相关特性。

Pin Statement 的基本语法:

PIN pinName

DIRECTION direction ;

USE useType ;

LAYER layerName ;

PORT

LAYER layerName ;

RECT (x1 y1) (x2 y2) ;

END

END PIN关键元素:

- Pin Name:

- 表示引脚的名称,例如

A、VDD、VSS等。

- 表示引脚的名称,例如

- DIRECTION direction:

- 指定引脚的方向。常见的方向有:

INPUT:输入引脚;OUTPUT:输出引脚;INOUT:双向引脚。

- 指定引脚的方向。常见的方向有:

- USE useType:

- 含义:

USE用于定义引脚的使用类型,通常用于指定引脚的功能。常见的USE类型包括:SIGNAL:普通信号引脚;POWER:电源引脚,通常用于连接电源网络;GROUND:接地引脚;CLOCK:时钟引脚。

- 示例:

USE SIGNAL ;表示这个引脚是一个普通信号引脚。

- 含义:

- LAYER layerName:

- 定义引脚所在的层,通常用于确定引脚的物理层级(如

M1、M2等金属层)。

- 定义引脚所在的层,通常用于确定引脚的物理层级(如

- PORT:

- 用于定义引脚的具体路径。路径由多个点和线段组成,用于描述引脚与其他区域的连接方式。

PORT下的LAYER定义了该引脚使用的物理层。 - RECT 表示连接路径,通常由一系列坐标点(如

(x1, y1)和(x2, y2))组成,定义了引脚的具体形状。

- 用于定义引脚的具体路径。路径由多个点和线段组成,用于描述引脚与其他区域的连接方式。

- MUSTJOIN:

- 含义:MUSTJION 用于指示某些引脚必须与其他引脚连接。在某些设计中,特定的引脚可能存在虚连情况,但在外部是需要连接在一起。了解更多,请点这里。

3.7 OBSTRUCTION

Obstruction 即 OBS,用于定义宏单元中的障碍区域,这些区域通常用于阻挡布线的进行。定义这些障碍的目的是确保在布局过程中,某些区域不会被布线覆盖,或者限制布线工具在这些区域中的活动。

OBS 语法说明:

OBS

{ LAYER layerName

[EXCEPTPGNET]

[SPACING minSpacing | DESIGNRULEWIDTH value] ;

[WIDTH width ;]

{ PATH pt ... ;

| PATH ITERATE pt ... stepPattern ;

| RECT pt pt ;

| RECT ITERATE pt pt stepPattern ;

| POLYGON pt pt pt pt ... ;

| POLYGON ITERATE pt pt pt pt ... stepPattern ;

} ...

| VIA pt viaName ;

| VIA ITERATE pt viaName stepPattern ;

} ...

END关键元素解释:

- LAYER layerName:

- 定义障碍所在的层,如

metal1、cut1等层。

- 定义障碍所在的层,如

- EXCEPTPGNET:

- 表示该障碍仅阻止信号网路的布线,而不影响电源网或接地网路的布线。这个选项通常用于减少干扰的区域,如敏感区域上方。

- SPACING minSpacing | DESIGNRULEWIDTH value:

- 指定障碍物的最小间距规则或设计规则宽度。如果使用

DESIGNRULEWIDTH,则该障碍的宽度会被视为此值进行间距检查。

- 指定障碍物的最小间距规则或设计规则宽度。如果使用

- WIDTH width:

- 用于指定障碍的宽度。如果未指定,通常使用默认宽度。

- PATH 和 RECT:

- 定义障碍区域的具体形状。

PATH定义路径,RECT定义矩形区域,POLYGON定义多边形区域。

- 定义障碍区域的具体形状。

- VIA:

- 定义VIA的位置,指定一个VIA或VIA数组,用于表示在障碍区域中的通孔。

- ITERATE:

- 用于重复定义形状或VIA,可以设置步进模式来指定重复的数量和间隔。

功能和应用:

- 阻挡布线:通常,

OBS用于在设计中定义不能进行布线的区域,帮助避免设计工具在这些区域进行不合规的布线。 - 通过引脚端口:尽管障碍物会阻挡布线,但如果引脚的端口与障碍物重叠,端口的几何形状将优先于障碍物。这意味着,引脚端口依然可以通过VIA或其他方式进行连接,即使它位于障碍物区域内。

例子:

OBS

LAYER metal1 ;

RECT 0 0 500 1000 ;

RECT 500 0 1000 500 ;

END这段代码定义了两个矩形障碍区域,位于 metal1 层。

Obstruction 用于定义宏中的障碍区域,以阻止布线工具在这些区域内布线。它有助于确保布局的规则得到遵守,特别是在设计中存在敏感区域或不允许布线的区域时。

4. 参考