版图中ERC类型如下:

4.MOS S/D power&ground checking

5.Gate directly connecting to power or ground checking

8. 总结

特别说明:以下文章中相关专有名词均以T家为例说明,不同厂商对应的名称叫法会存在差异,请知悉!

下面将分别介绍每个ERC类型:

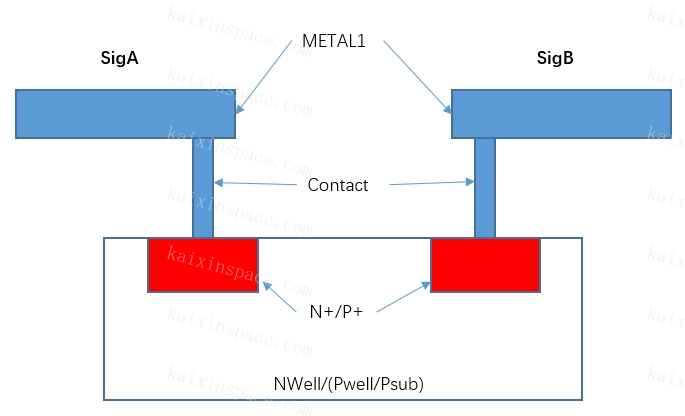

1. Soft connect checking

Nwell和Pwell/Psub都是高阻的材料

如上图所示会出现两种错误识别:

- 假设SigA和SigB为同一个net(Short)时;错误举例:如果SigA是一个电源net,由于Nwell或Pwell/Psub可看成是高电阻,所以此时IR drop会非常严重,以至于SigA和SigB几乎开路。和假设冲突,故错误。

- 假设SigA和SigB是两个不同net(Open)时;错误举例:如果SigA是一个电源net,SigB是一个地net,那么很明显它们将短路(衬底Bulk始终是连在一起的)。和假设冲突,故错误。

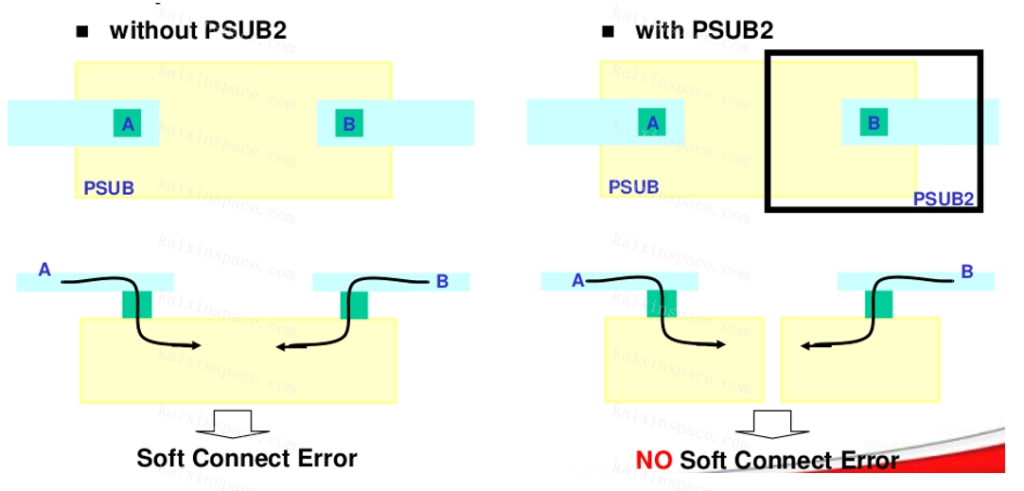

版图中常出现soft connect情况:当有两个不同的gnd时,需要用psub2覆盖,不然会出现错误。

如存在上述图示情况,会出现如下ERC错误:

- Check SOFTCHK nxwell

- Check SOFTCHK psub

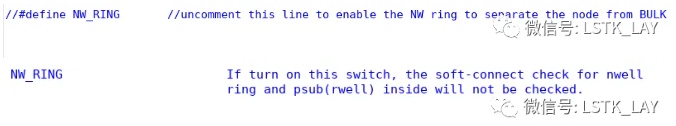

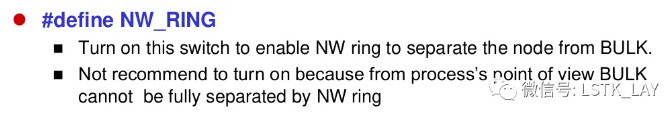

LVS rule中相关soft connect checking的Switch命令:

2.Path checking

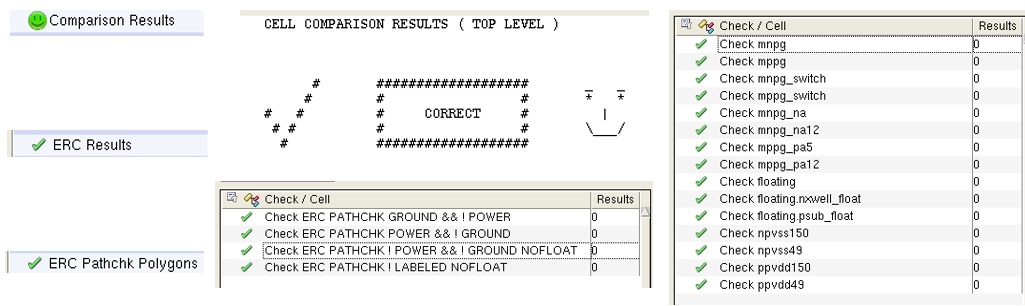

此ERC类型主要检查以下四种情况:

1. Nodes with a path to power but not ground

2. Nodes with a path to ground but not power

3. Nodes without a path to both power and ground

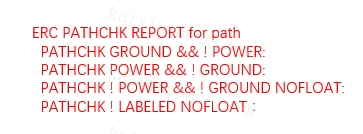

4. Nodes without a path to pin对应错误报告如下:

错误报告中相关名词解释:

1. POWER:Reports nets with a path to a power net

2. !POWER:Reports nets with no path to a power net

3. GROUND:Reports nets with a path to a ground net

4. !GROUND:Reports nets with no path to a ground net

5. !LABELED: Reports nets with no path to any labeled net

6. NOFLOAT: Express ignore floating net

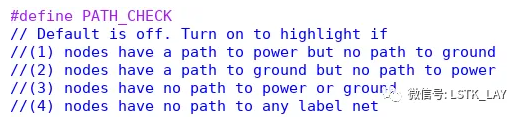

7. “&&”相当于“AND”LVS rule中相关Path checking的Switch命令:

3.ptap/ntap checking

此项检查ptap/ntap是否正确接到电源和地。

ptap 需要正确接到gnd;

ntap 需要正确接到power;

否则会报出如下ERC错误:

- Check ERC errors “PPVDD49” for PTAP

- Check ERC errors “NPVSS49” for NTAP

LVS rule中相关ptap/ntap checking的Switch命令:

4.MOS S/D power&ground checking

此项检查NMOS或PMOS,当漏(drain)或源(source)其中一端接Power而另一端接Gnd的情形。

如存在以上情形,会出现如下ERC错误:

- Check ERC errors“mppg” for PMOS

- Check ERC errors“mnpg” for NMOS

LVS rule中相关ptap/ntap checking的Switch命令:

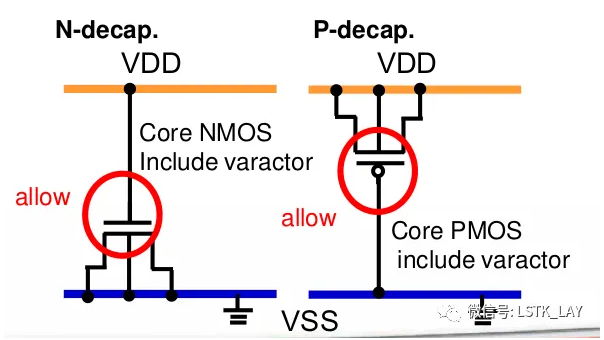

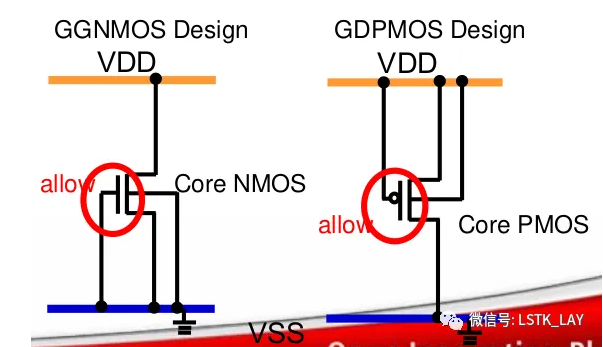

5.Gate directly connecting to power or ground checking

此项检查MOS gate 是否正确连接。有2种情况会被识别错误:

- Core voltage MOS gate 直接连接到Power,漏或源连接到Gnd;

- Core voltage MOS gate 直接连接到Gnd,漏或源连接到Power;

注意:Core voltage MOS gate仅仅指Thin gate(OD),不包含高压(Thick gate)OD2的MOS;

如违反,将会出现以下ERC错误:

- Check ERC errors“ppvdd150” for PMOS gate

- Check ERC errors“npvss150” for NMOS gate

注意:以下2种情况属于特殊案例,将不做此项ERC检查:

1、MOS当作去耦电容使用(如下图所示)

2、GGMOS case 和 GDPMOS case(如下图所示)

LVS rule中相关gate checking的Switch命令:

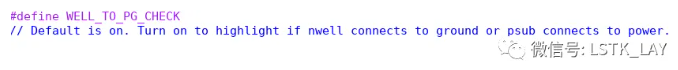

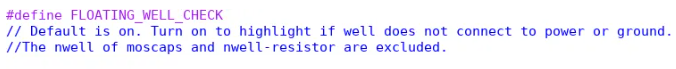

6.Floating well checking

此项检查阱(Well)是否正常被接到相关电源和地。

NWell需要正确接到Power;

Psub/Pwell需要正确接到Gnd;

否则会报出如下ERC错误:

- Check ERC error“floating.nwell”

- Check ERC error“floating.psub”

LVS rule中相关Floating well checking的Switch命令:

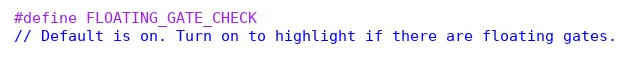

7.Floating gate checking

此项检查gate没有连接到任何net,如存在此情况会报如下ERC错误:

Check ERC errors“floating” LVS rule中相关Floating gate checking的Switch命令:

8. 总结

- 每个Soft connect error 必须被修复;

- 每个ERC errors/warnings需要和电路设计者一起确认;

—END—