背景介绍:发现网络上大多数都是介绍Latch up 原理的文章(当然站长也有写过:请参考本站文章:一文搞懂闩锁效应(Latch up)),但很少看到介绍具体latch up规则使用的相关文章;于是,便有想法写一篇关于latch up规则的文章,以给需要的人提供些许参考。

2025.12.12:增加第三节中 Tips2 内容;

正文开始时的一些说明:

(1)本文内容及相关专业术语均来自TSMC家工艺,不同厂家工艺名称可能有所不同。使用不同工艺的人员,也可参考本文。千举万变,其道一也!

(2)本文所述的内容,在厂商提供的规格书中,均能找到,并设有专门章节讲解;

(3)对于文中内容如有疑问,请以规格书为准。

1. Latch up 规则检查前的一些概念名称和解释

1.1 PAD主要分为两大类:

信号PAD,常见简称:IO PAD

电源地PAD,常见简称:VDD PAD和VSS PAD

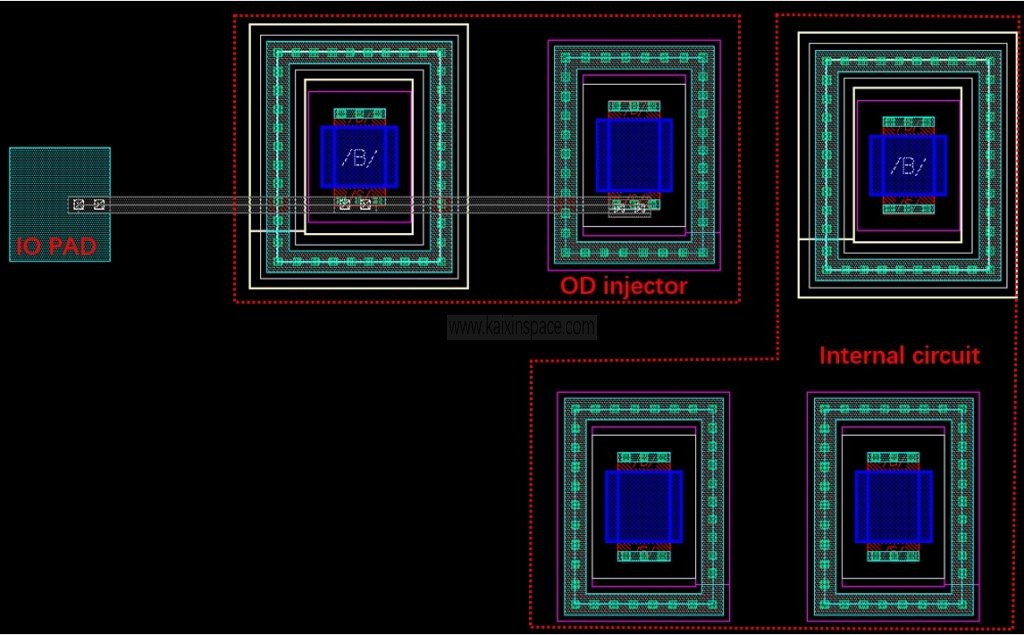

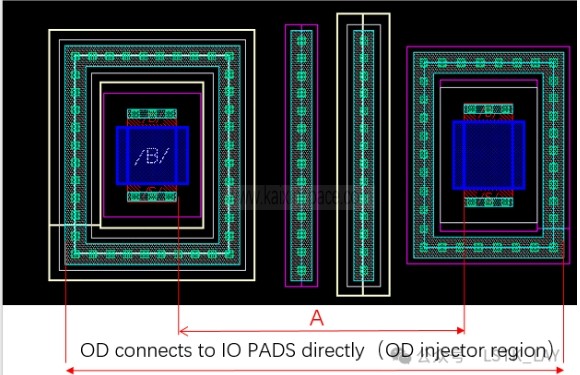

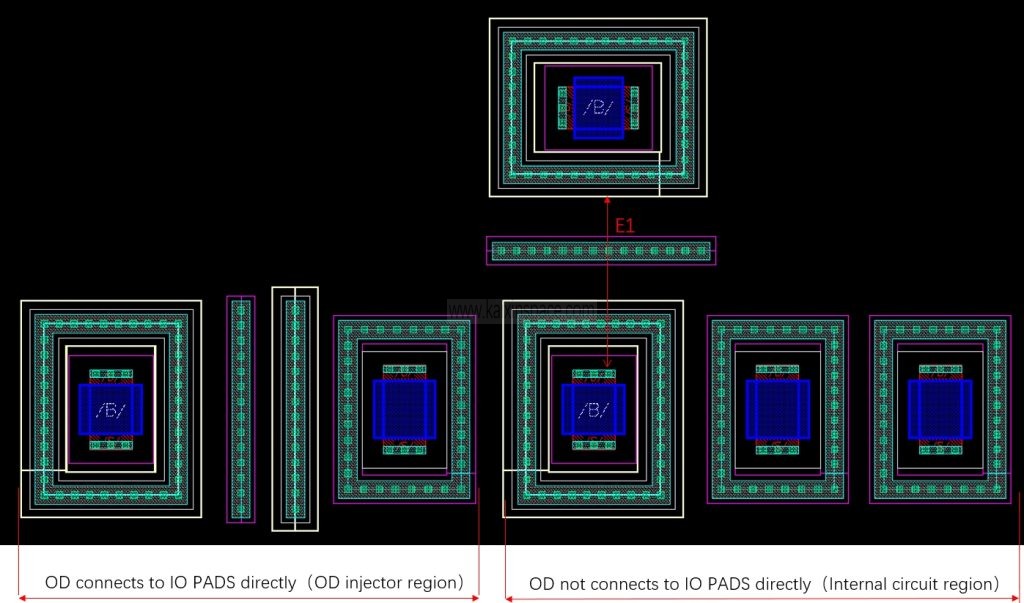

1.2 内部电路(Internal circuit)(见图1)

指不和IO PAD直接相连的器件;包括NMOS、PMOS、Capacitors、varactor;

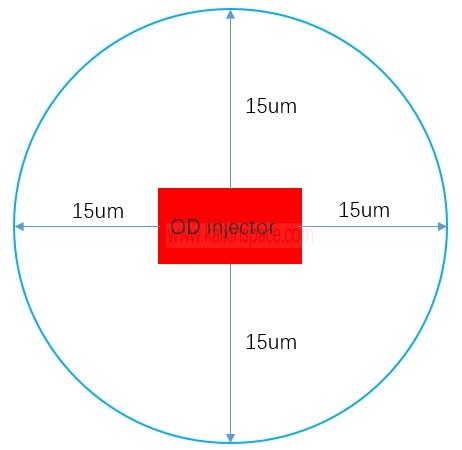

1.3 有源区注入(OD injector)(见图1)

指任何直接连接到IO PAD有源区都被视为OD injector;

Tips1:有源区注入,会分不同电压等级,如:1.1V 1.5V 1.8V 2.5V 3.3V 5V 等等,具体请参考对应工艺规格书;

Tips2:OD injector和Internal circuit概念很重要,请务必理解!

注意:为方便理解,图中标出的OD injector区域为示意区域,真实的OD injector区域是指具体的有源区(OD)。

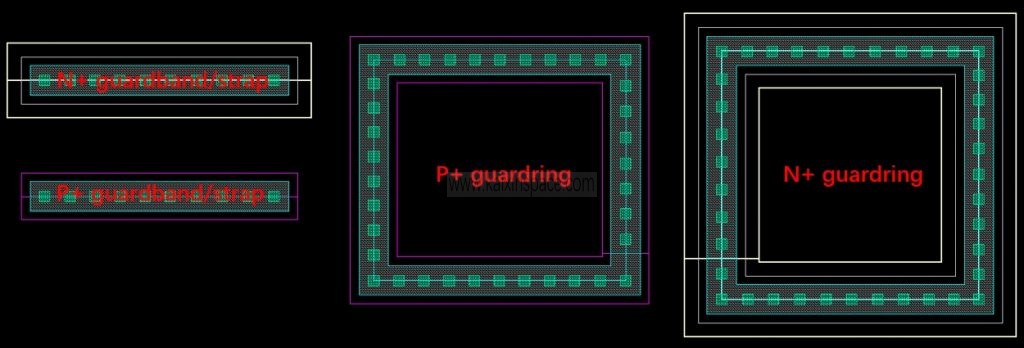

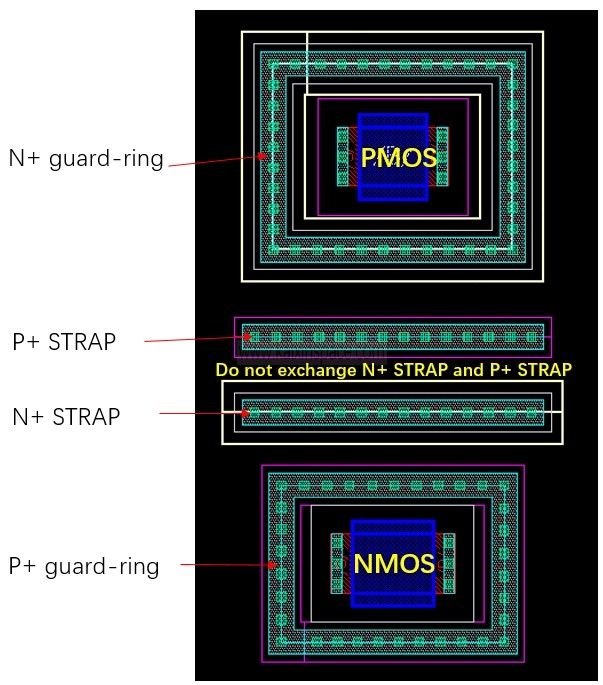

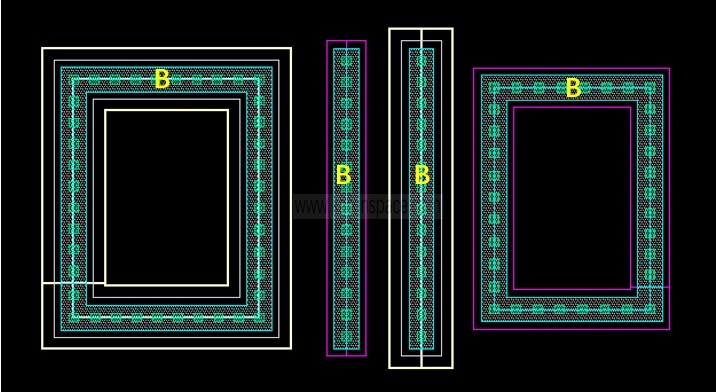

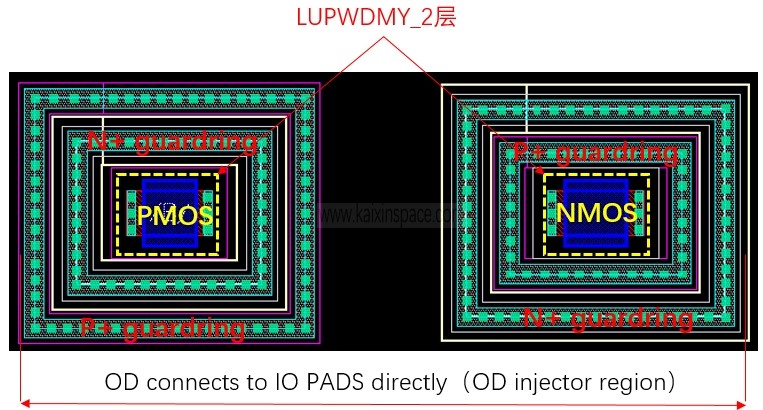

1.4 保护环(Guardring)(见图2)

指一个完整的环,环不能有破损;分为N+ guardring和P+ guardring;

1.5 保护带(guardband/strap)(见图2)

指一个保护带,不是完整的环;分为N+ guardband/strap和P+ guardband/strap;

2. Latch up 中可能用到的几个标识层

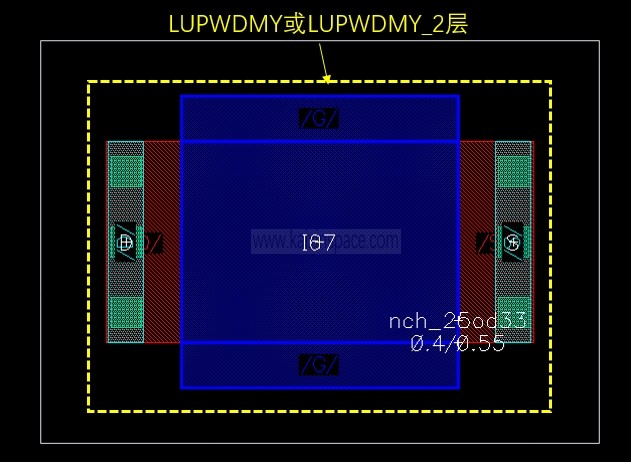

2.1 LUPWDMY层:用来waive一些LUP的规则,需要user手动放置;

2.2 LUPWDMY_2层:用来触发检查Area IO(AAIO)相关的latch up规则,同样需要user手动放置;

上述两层常见的用法是:将对应OD区域用对应的层框住即可。

2.3 RES200层:用来识别电阻后面的器件是否属于OD injector,如果相关电阻上覆盖了此层,那么电阻后面的器件将不被识别为OD injector。(后文有对”RES200层”做详细介绍)

对于DRC如何进行latch up 规则检查,让我们继续往下看。

3. Latch up 规则检查流程介绍(或叫执行步骤)

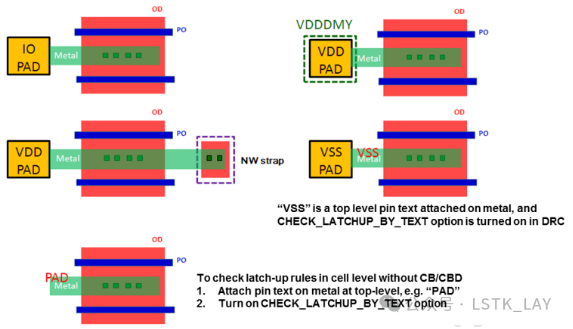

步骤1:首先要准确识别出PAD类型,是IO PAD还是VDD/VSS PAD;

有以下三种方法识别成电源地PAD:

(1)默认情况下,DRC识别电源地pad,根据顶层PAD连接到的保护带/环(guardring/strap/band)的net来识别,会将这些PAD识别为电源地PAD;

(2)DRC将盖有”Power Dummy Layer”的识别层,作为电源地PAD;

常见的”Power Dummy Layer” 的识别层有:VDDDMY、VSSDMY。

注意:不同工艺可能名称不一样,请参考对应工艺的规格书。

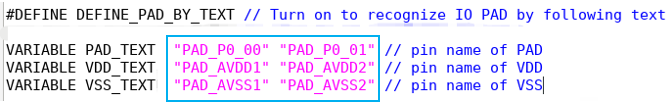

(3)DRC规则文件中,有相关定义”PAD_BY_TEXT”的开关;如果需要请在规则文件中打开对应开关。

识别成IO PAD:未被上述3种方式识别的PAD,均视为IO PAD。

Tips1:在cell level层次下 ,如果想将某段metal定义为pad,请在此metal上打上“PAD”标识,并打开”DEFINE_PAD_BY_TEXT”开关。这样就可以模拟顶层PAD连接情况,并清除在top层可能出现的LUP规则问题。

Tips2:推荐打开 “DEFINE_PAD_BY_TEXT” 开关,并写出对应项目中实际用到的 IO PAD 和 PWR/GND PAD, 请参考下图:(2025.12.12 updated)

步骤2:当IO PAD被准确识别出来后,DRC就需要开始识别与IO PAD 相连器件(OD injector)与不相连的器件(internal circuit),从而进行相关规则检查。

以下是DRC规则中提供的几种区分OD injector和internal circuit的方式:

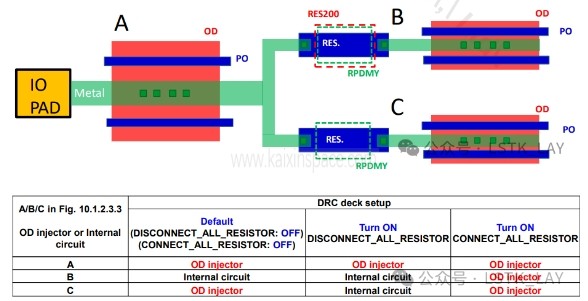

DRC规则文件中有提供两个开关(如下)和一个特殊的层(RES200)。

1. DISCONNECT_ALL_RESISTOR

2. CONNECT_ALL_RESISTORTips1:在实际使用中,这两个开关要么都关闭,要么只能开其中一个,如果两个开关都打开的情况下,“DISCONNECT_ALL_RESISTOR”将具有高优先级;

Tips2:特殊层(RES200)需要user手动放置,另外只有当上述两个开关都关闭的情况下,”RES200层”才会起作用;相反,只要上述两个开关其中一个打开,RES200层都将失效;

Tips3:当使用的工艺(T22nm),电路中存在TFR(Thin Film Resistor)电阻器件时,电阻后面的器件均会被识别为OD injector,此时两个DRC的开关和RES200层均失效。

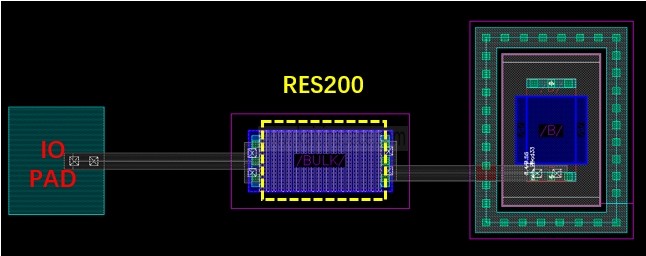

(1)首先对RES200层进行讲解

注意:此时”DISCONNECT_ALL_RESISTOR”和”CONNECT_ALL_RESISTOR”开关均处于关闭状态。

IO PAD附近结构:当PAD通过一个电阻(R)连到内部时;

a:如果R>=200ohm时,此时出现latch up风险低,此时将”RES200层”手动覆盖住电阻区域(RPDMY),电阻后面的器件将被视为:Internal circuit部分;

b:如果R<=50ohm时,此时出现latch up风险高,此时电阻后面的器件将被视为:OD injector部分;

c:如果50ohm<R<200ohm时,此时依设计决定是否将电阻后的器件视为Internal circuit或OD injector部分。

(2)再对”DISCONNECT_ALL_RESISTOR”和”CONNECT_ALL_RESISTOR”开关进行说明;

a:当”DISCONNECT_ALL_RESISTOR”开关被打开时,电阻后面的器件将都被视为:Internal circuit;

b:当”CONNECT_ALL_RESISTOR”开关被打开时,电阻后面的器件将都被视为:OD injector;

一系列的Latch up DRC识别动作结束,接下来让我们开始LUP相关规则的检查。

步骤3: 开始一系列的latch up规则检查;

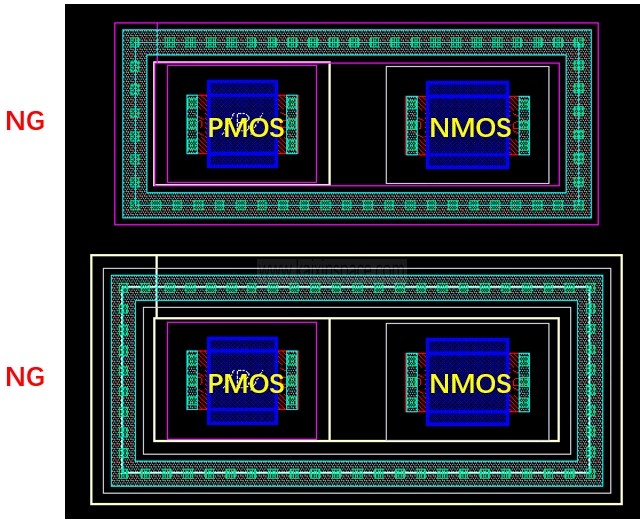

3.1 LUP.1 类规则检查

检查对象:被视为OD injector的部分。

检查内容:

(1)任何的N+ OD都必须被P+ guardring围绕;或者任何P+ OD都必须被N+ guardring围绕;

(2)额外再增加N+ STRAP 和 P+ STRAP(如下图所示),作为更进一步预防。(DRC推荐做法)(LUP.9g)

以下情况将忽视LUP.1类规则检查

- 被LUPWDMY层覆盖的OD injector部分。

Tips1:推荐额外增加的strap,不做强制要求;根据具体版图设计选择性添加;

Tips2:不同类型的管子,不能同时被同一种类型的guardring包围。

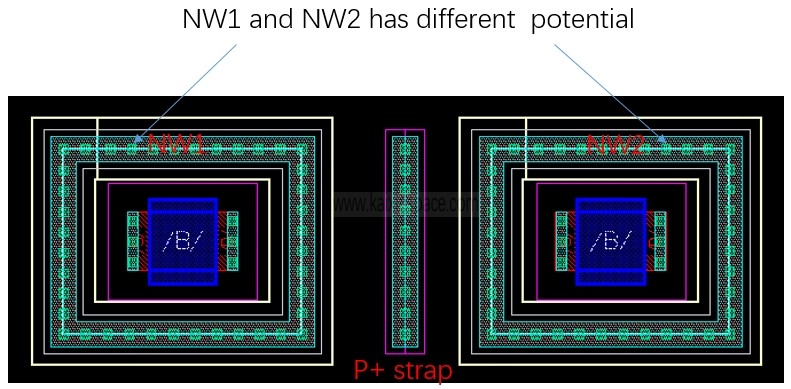

3.2 LUP.2类规则检查

检查对象:对距离OD injector区域15um范围内的MOS OD;

检查内容:

(1)对上述检查对象进行LUP.1检查;

(2)当一个NW靠近另外一个具有不同电位的NW(PMOS),一个P+ STRAP建议被插在这两个NW之间。(如下图)(DRC推荐做法)

以下几种情况将不进行LUP.2的规则检查。

- MOS OD是浮空的,没有任何contact连接到gate或者S/D级;

- MOS OD有被LUPWDMY层覆盖的;

- 含有DNW的NMOS管,此管子DNW上方的NW和附近NW(PMOS围绕的guardring)没有物理交叉(physically interact),并且管子DNW或NW上的电位要大于等于附近NW上的电位。

3.3 LUP.3类规则检查

检查对象:被视为OD injector的部分;

检查内容:NMOS和PMOS之间有源区的距离A,需要满足一定距离要求;不同电压的管子,两个有源区的距离A是变化的,电压越高,A的值要求就越大;具体,请参考相关工艺规格书。

Tips:不同宽度的guardring对应距离A要求也会有所不同。

以下几种情况将不进行LUP.3的规则检查。

- 被LUPWDMY层覆盖的OD injector部分;

- 含有DNW的NMOS管,此管子DNW上方的NW和附近NW(PMOS围绕的guardring)没有物理交叉(physically interact),并且管子DNW或NW上的电位要大于等于附近NW上的电位。

3.4 LUP.4规则检查

检查对象及内容:OD injector区域以及距离此区域15um以内的guardring或STRAP中的OD宽度B都要大于等于一定值。

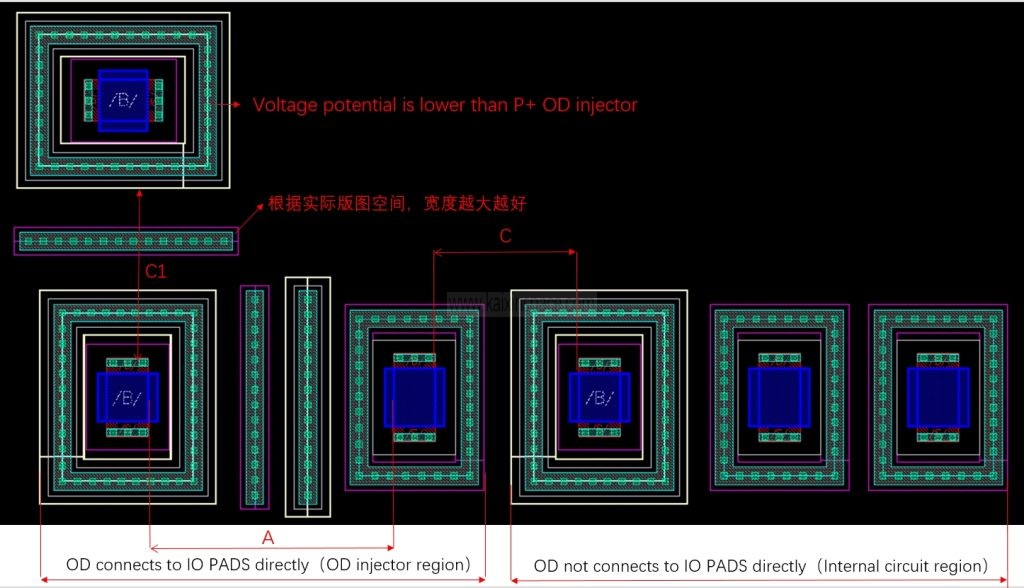

3.5 LUP.5类规则检查

检查对象:OD injector区域的OD与距离OD injector区域15um内的OD(Internal circuit区域);

检查内容:

(1)OD injector区域的N+ OD 与internal circuit 区域PMOS的P+ OD之间的距离C;或者OD injector区域的P+ OD 与internal circuit 区域NMOS的N+ OD之间的距离C的值。

(2)OD injector区域的NW和附近不同电位的NW,需要检查OD injector区域P+ OD到附近NW的距离C1,而且C1的距离随着两个NW的电压差增大而增大。(DRC推荐)

以下情况将不进行LUP.5的规则检查

- 含有DNW的NMOS管,此管子DNW上方的NW和附近NW(PMOS围绕的guardring)没有物理交叉(physically interact),并且管子DNW或NW上的电位要大于等于附近NW上的电位。

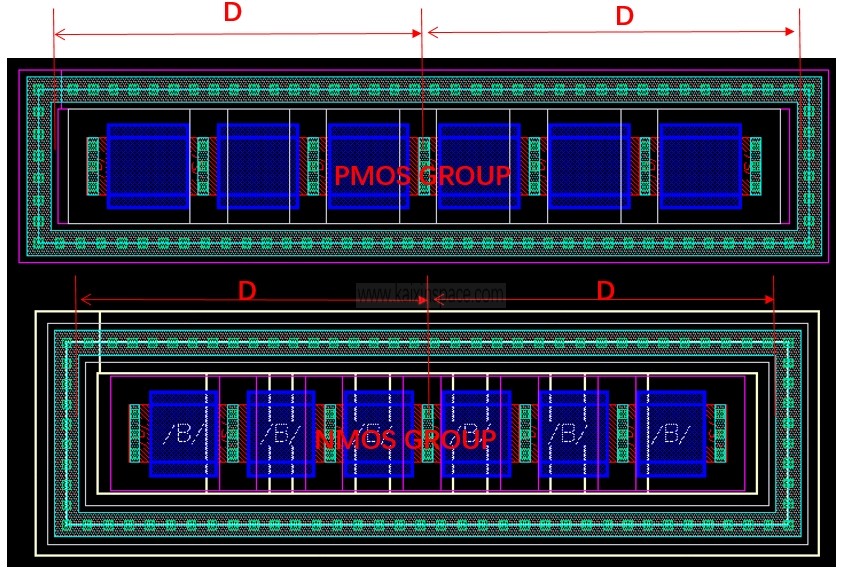

3.6 LUP.6规则检查

检查对象:OD injector区域的OD与internal circuit区域的OD;

检查内容:在相同的阱中,以任意PMOS的source/drain端为中心,在距离D(30/40um)内,要能找到NW STRAP或者N+ guardring;反之,以任意NMOS的source/drain端为中心,在距离D(30/40um)内,要能找到PW STRAP或者P+ guardring;否则报LUP.6错误。

3.7 LUP.7规则检查(推荐检查)

检查对象:对距离OD injector区域15um范围内的MOS OD;

检查内容:Internal circuit区域的NW和附近不同电位的NW,需要检查Internal circuit区域P+ OD到附近NW的距离E1,而且E1的距离随着两个NW的电压差增大而增大。

4. 问题与讨论

问题1:什么是Area IO(AAIO)?

Ans:Area IO 是一种特殊的IO(一般用在超大规模集成电路中或者需要高性能的电路中),主要放在核心电路附近,为了减少信号传输距离,可以保证核心电路具有较低的噪声和好的信号和电源完整性。相对于传统的Peripheral IO放在芯片外围,信号传输距离长,更适合传统较低复杂的设计中。

问题2:在文章中2.2小节有提到Area I/O(AAIO),那和AAIO相关的latch up规则也是遵循上述列出的几类LUP.x规则吗?

Ans:AAIO相关的latch up规则同样会检查上述几类规则中的几种,但相关距离均会要求更加严格,具体请参考相关规格书。值得注意的是:在AAIO的LUP规则中,LUP.14规定需要对和IO PAD相连的OD injector区域,围绕双环(如下图)。另外对于双环的OD宽度也有一定要求,具体数值,请参考对应规格书。

5. Reference

【1】TSMC相关工艺规格书。

千举万变,其道一也!:出自《荀子·儒效》,与时迁徙,与世偃仰,千举万变,其道一也。意思是,形式无论如何变化都是依照一个规则、中心或是基础,缺少这个规则、中心、基础,那么事物就不会存在,原则始终如一。