本文始于2024年05月,文章中介绍了在芯片版图中什么是天线效应,并且详细介绍了天线比率计算的方式和版图中避免天线效应的几种方法,以给需要的人提供些许参考。后于2025年02月进行第一次更新。

2025年02月更新:

- 在3.2小节增加计算天线比率算法的图示,以方便读者理解;

- 增加3.3小节

1. 什么是天线效应(Antenna Effect)

在芯片生产过程中,暴露的金属线或者多晶硅(polysilicon)等导体,就像是一根根天线,会收集电荷(如等离子刻蚀产生的带电粒子)导致电位升高。天线越长,收集的电荷也就越多,电压就越高。若这片导体碰巧只接了MOS 的栅,那么高电压就可能把薄栅氧化层击穿,使电路失效,这种现象我们称之为“天线效应”。随着工艺技术的发展,栅的尺寸越来越小,金属的层数越来越多,发生天线效应的可能性就越大。

2. 天线效应形成的机理

在深亚微米集成电路加工工艺中,经常使用了一种基于等离子技术的离子刻蚀工艺(plasma etching)。此种技术适应随着尺寸不断缩小,掩模刻蚀分辨率不断提高的要求。但在蚀刻过程中,会产生游离电荷,当刻蚀导体(金属或多晶硅)的时候,裸露的导体表面就会收集游离电荷。所积累的电荷多少与其暴露在等离子束下的导体面积成正比。如果积累了电荷的导体直接连接到器件的栅极上,就会在多晶硅栅下的薄氧化层形成F-N 隧穿电流泄放电荷,当积累的电荷超过一定数量时,这种F-N 电流会损伤栅氧化层,从而使器件甚至整个芯片的可靠性和寿命严重的降低。在F-N 泄放电流作用下,面积比较大的栅得到的损伤较小。因此,天线效应,又称之为“等离子导致栅氧损伤(plasma induced gate oxide damage)

3. 天线效应的量化

3.1 天线比率(Antenna Ratio)相关定义

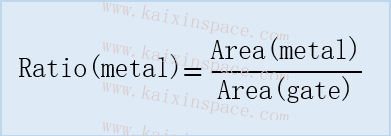

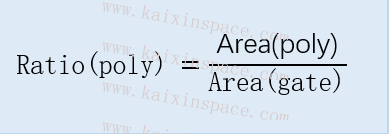

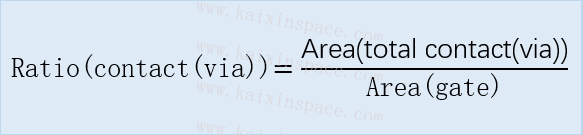

通常情况下,我们用“天线比率(antenna ratio)”来量化天线效应发生的几率。一共有三类(metal、poly、Via),分别如下:

“天线比率(antenna ratio)定义:

Ratio(metal)=Area(metal)与 Area(gate)的比值

Ratio(poly)=Area(poly)与 Area(gate)的比值

Ratio(contact(via))=Area(total contact(via))与 Area(gate)的比值

其中:

Area(metal):指与栅极相连的金属面积;

Area(poly):指与栅极相连的多晶硅(Polysilicon)面积;

Area(total contact(via)):指总共的过孔面积,包含contact孔面积;

Area(gate):MOS管的栅面积。

3.2 两种计算天线比率的方法

在实际应用中,天线比率的计算会有如下两种场景:

- Net 连接 Diode(OD)场景

- Net 不连接 Diode(OD)场景

(1)在”Net 不连接 Diode(OD)”这种场景中;

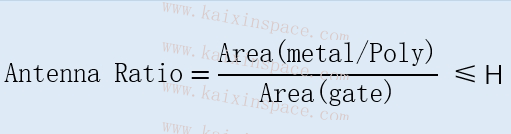

天线比率规则定义为:

其中:H为厂商手册中定义的参数,如果计算的结果大于此值,则表示违反了天线的规则。

(2)在”Net 连接 Diode(OD)”场景中;

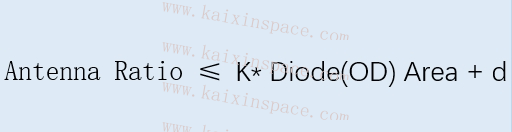

天线比率规则定义为:

其中:K、d 均为厂商手册中定义的定值参数。

根据不同工艺和不同要求,在算法、面积计算方式会有所不同;

(1)常见的两种算法模式

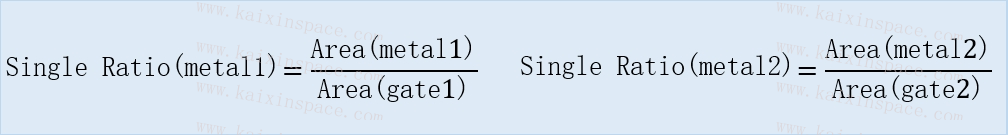

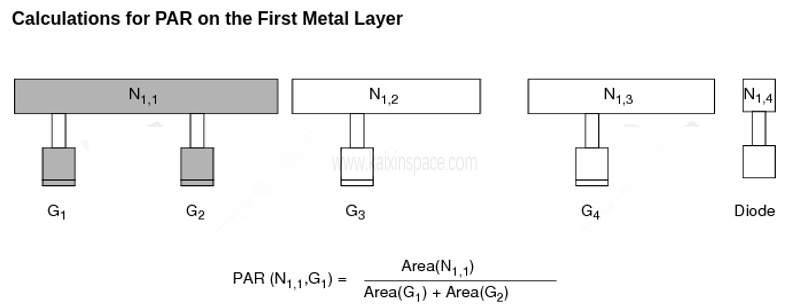

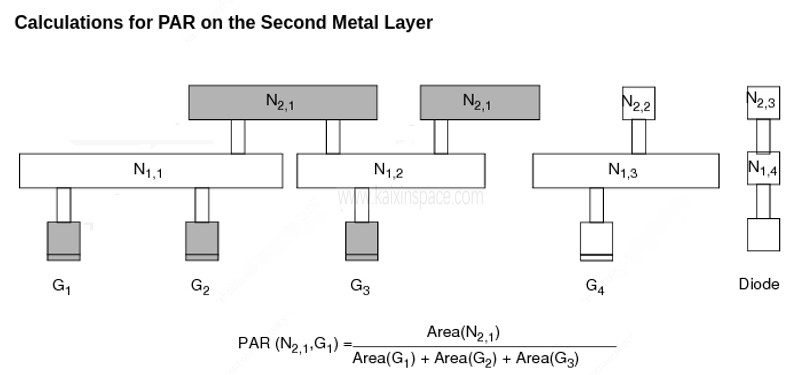

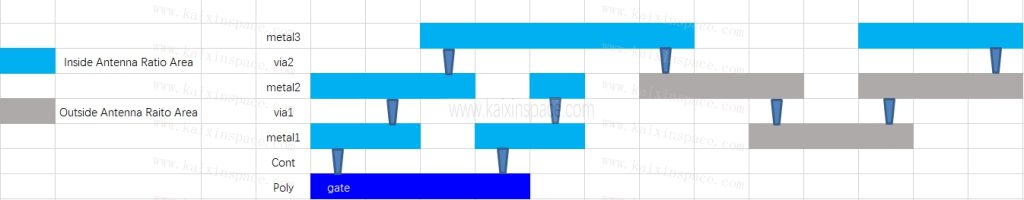

- Single Layer mode(或者叫:PAR—Partial Antenna Ratio)

计算的是单个net每层metal或Poly的面积与相连gate面积的比值;

例如:当检查M1层的天线比率时,会单独把M1层的面积除以与其相连的gate面积;当检查M2层的天线比率时,会单独把M2层的面积除以与其相连的gate面积,以此类推。

检查第n层metal时,可以写成如下表达式:

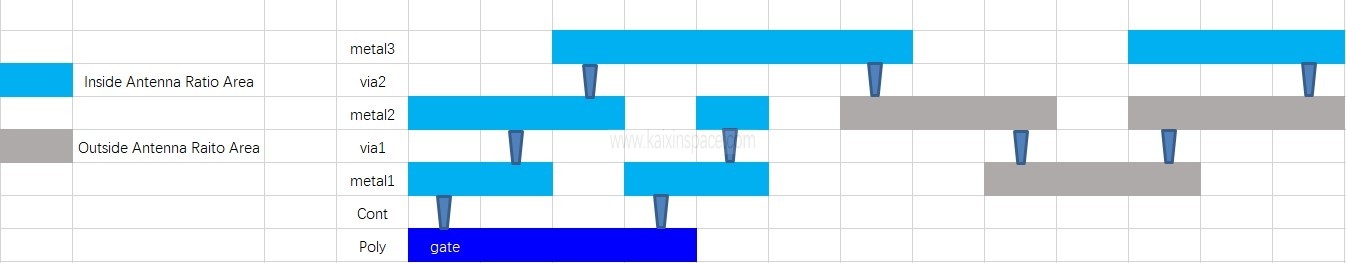

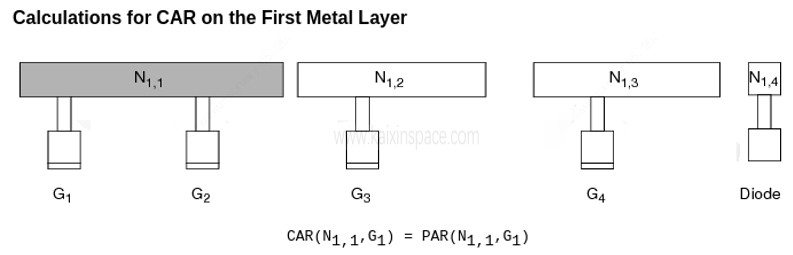

为方便理解单层的计算模式,增加相关图片说明(阴影部分),如下:(2025年02月新增)

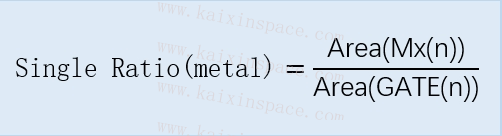

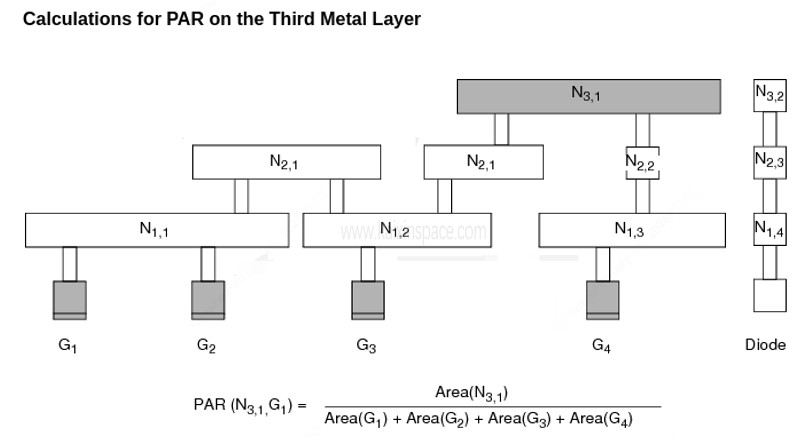

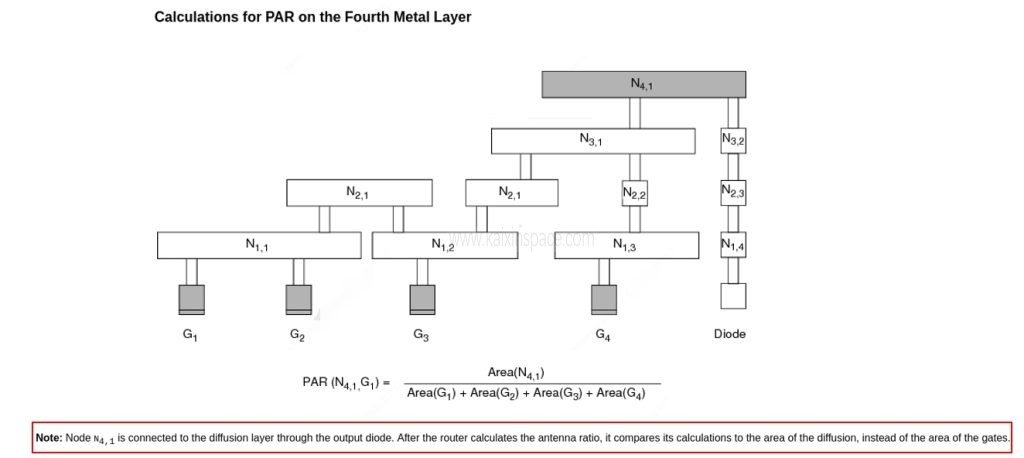

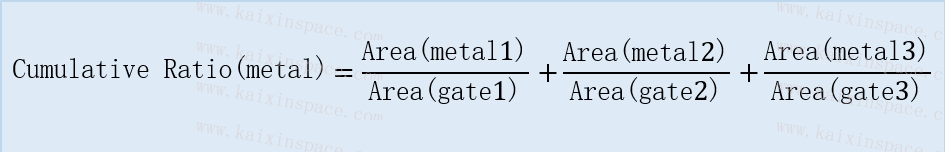

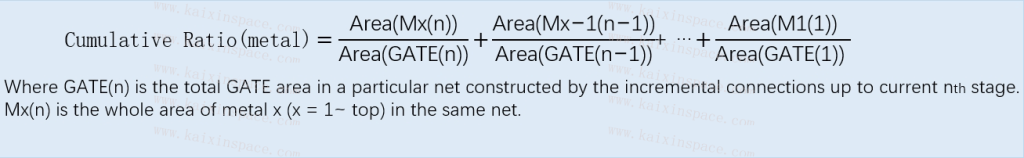

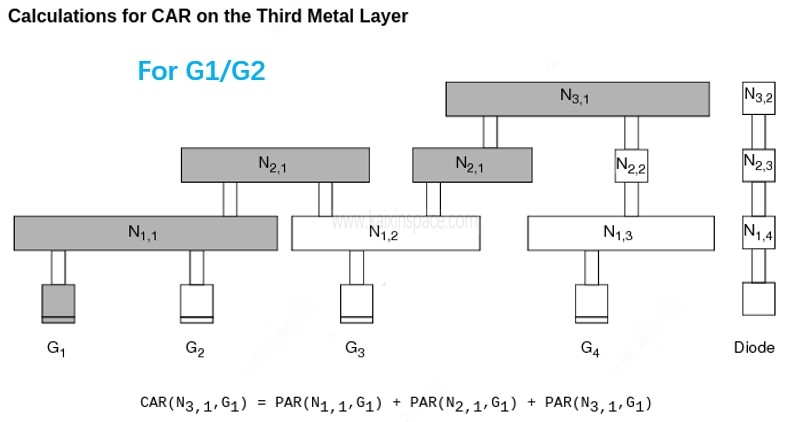

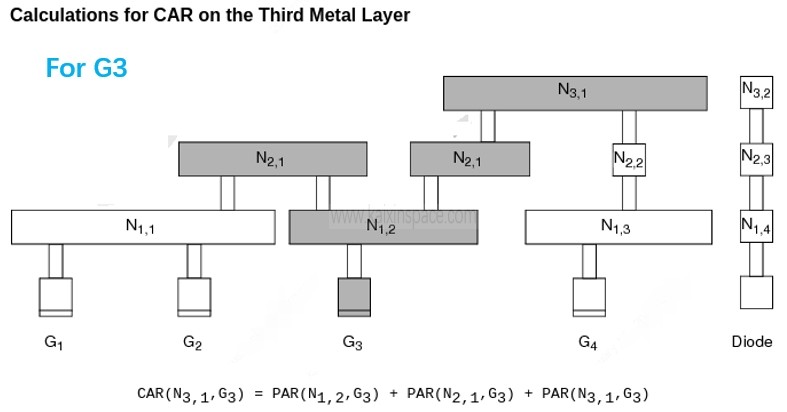

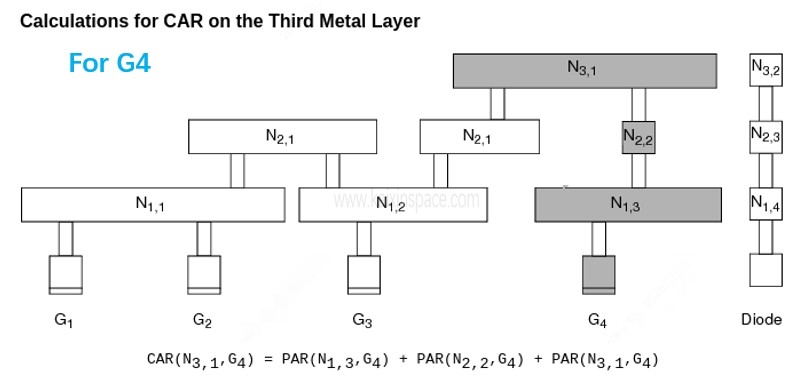

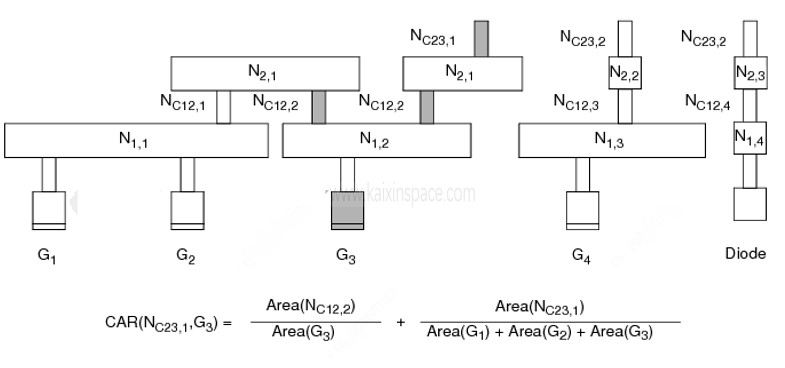

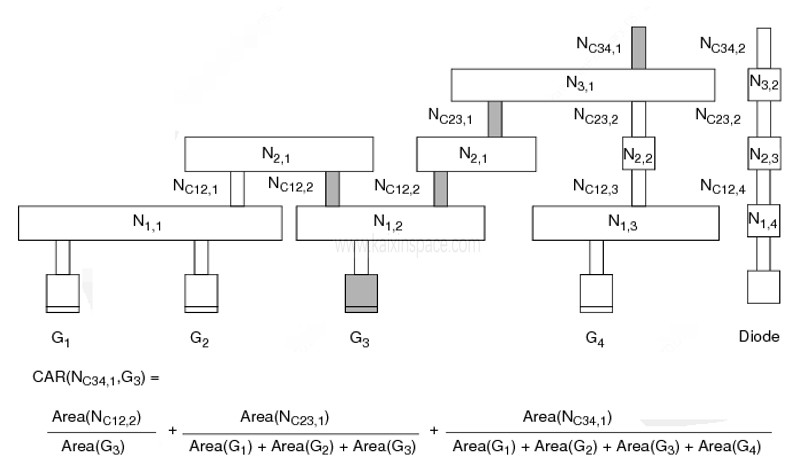

- Cumulative mode (累积天线效应),(或者叫:CAR—Cumulative Antenna Ratio )

即分别计算出不同层metal面积对gate面积的比值,然后再相加;

例如:当检查M3层的天线比率时,会分别计算M1层面积与其相连gate面积的比值,然后在计算M2层面积与其相连gate面积的比值,然后在计算M3层面积与其相连gate面积的比值,最后将这些比值相加得到最终的天线效应比率值,如下表达式:

对于检查第n层的天线比率时,可写成如下表达式:

为方便理解累积的计算模式,增加相关图片说明(阴影部分),如下:(2025年02月新增)

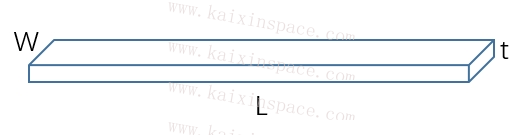

(2)常见的两种面积计算方式

- Top Area 方式

指的是图形的长度与宽度的乘积;

即:Area=L x W

- Perimeter(Sidewall) Area 方式

指的是图形的周长(侧墙)与厚度的乘积;

即:Area=2x[(L+W)xt]

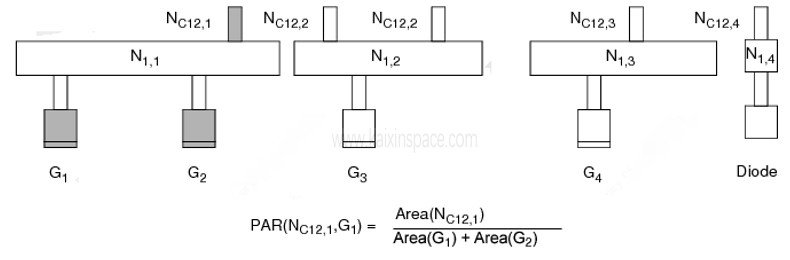

3.3 计算过孔(CO与Via)的天线比率 (2025年02月新增)

(1)以单层模式的算法计算过孔的局部天线比率,即:PAR—Partial Antenna Ratio,见下图;

(2)以累积模式的算法计算过孔的天线比率,即:CAR—Cumulative Antenna Ratio,见下图;

4. 天线效应解决的几种方法

4.1 跳线法

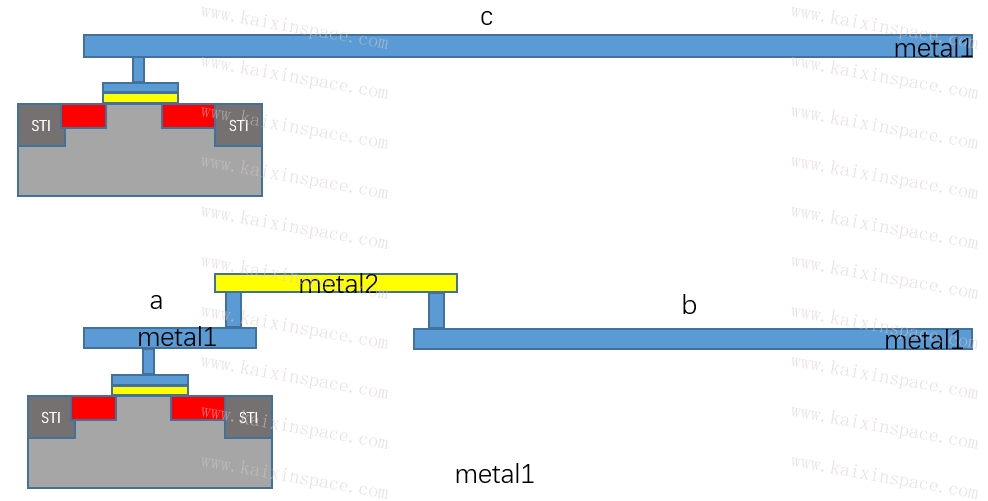

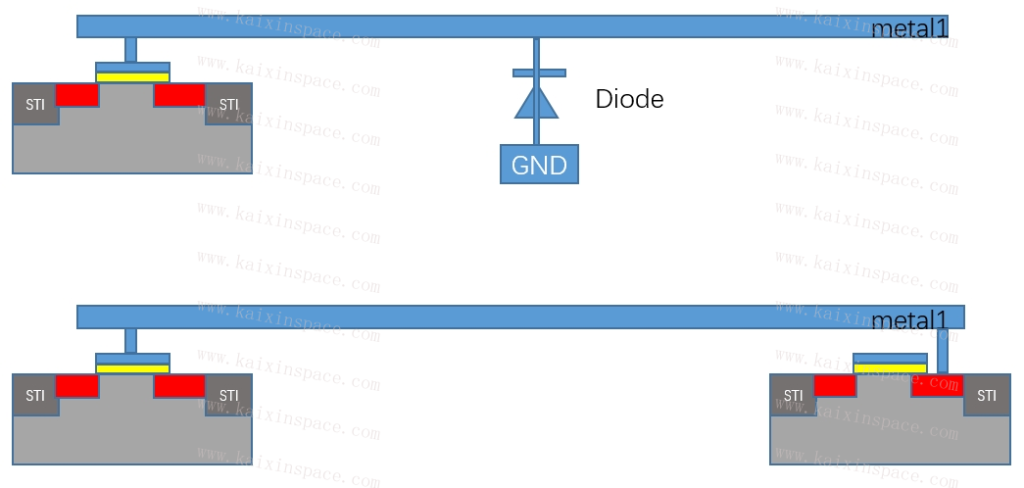

4.1.1 向上跳线

在实际芯片生成过程中,我们都知道metal和via的制造是从下往上制作的,并且做完一层都会有放电步骤(会放电掉一大部分电荷,但仍然会残留一部分电荷),当我们采用向上跳线时,可以明显看到当前层的面积被减小了(此时上层还不存在),如下图,线长从原来有效长度c变成了现在的有效长度a,故解决了天线效应。

注意:向上跳线的位置尽可能靠近gate。

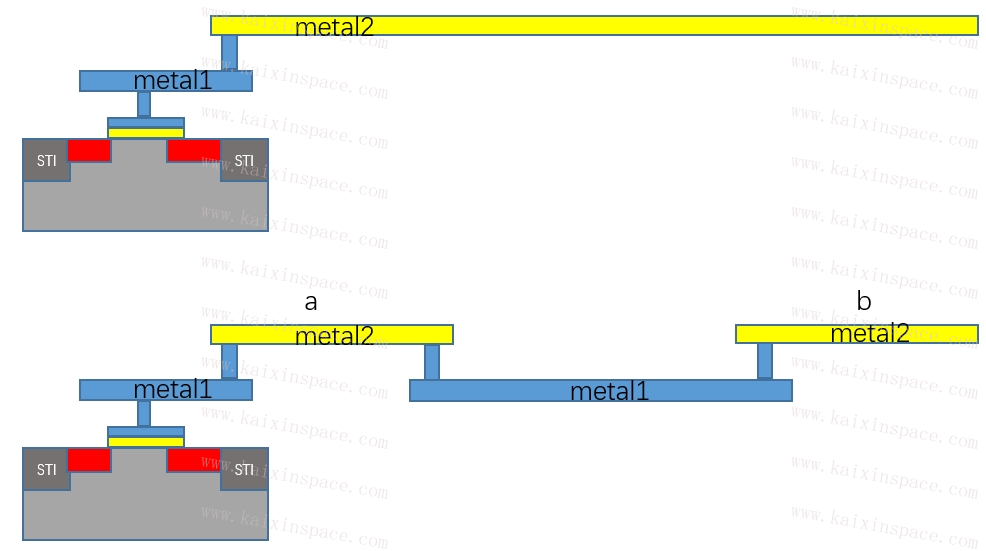

4.1.2 向下跳线

在特定的情况下,向下跳线同样可以解决天线效应问题,但效果往往没有向上跳线有效。如下图,当metal2违反天线效应时,即使向下跳线,但a段和b段依然会被计算为有效面积,所以此时可能需要向下跳线的线段很长,才能解决metal2违反天线效应,在一些空间有限的案子中很难满足,故Case by Case。

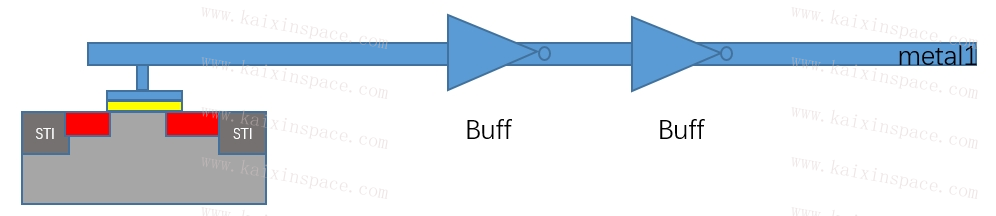

4.2 增加反偏Diode

引入反偏diode(靠近gate)本质是提供了积累电荷的泄放路径,是最有效且最直接的方法,同时也是厂商推荐的方法。

注意:将net接到MOS的source、drain或Strap areas也同样可以起到防止天线效应的作用。

4.3 增加buff器件

增加buff器件(靠近gate)本质是增加了gate的面积、减小了metal的面积,也可以有效防止天线效应的产生。对于加buff办法是否影响信号质量,需要电路设计者确认。

5. 问题与讨论

5.1 Antenna rules 是如何做到一层一层的计算天线比率的?

Ans:在ant.drc rule 文件中会有如下语句定义逐层检查:

DRC INCREMENTAL CONNECT YES5.2 在版图设计中哪些情况会进行antenna rule 检查?

Ans:常见有以下几种情况:

(1)面积过大的metal、Poly线 或 Contact/Via孔;

(2)版图中有MIM电容相关的地方;

(3)版图中有DNW相关的地方;

5.3 如果顶层出现antenna ratio 违反时,应该怎么处理呢?

Ans:如果顶层出现问题,首选增加diode来解决(推荐);又或者向下跳线(不推荐)。

5.4 在进行antenna ratio 计算时,如何确认相同net在不同层的有效面积?

Ans:请参考下图。

-END-

参考资料:

【1】The Art of Analog Layout ,Second Edition——Alan Hastings

【2】天线效应_百度百科 (baidu.com)

【3】LEF/DEF 5.8 Language Reference