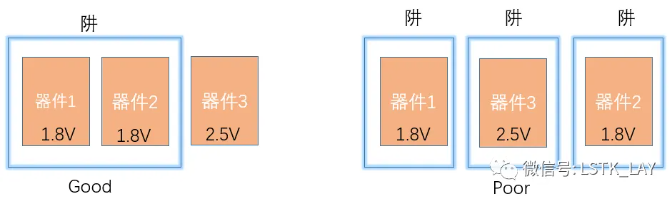

1. 阱邻近效应

1.1 阱邻近效应(Well Proximity Effect,WPE)

是指在先进工艺技术下,靠近阱边缘的器件的电特性会受到器件沟道区域到阱边界距离的影响。

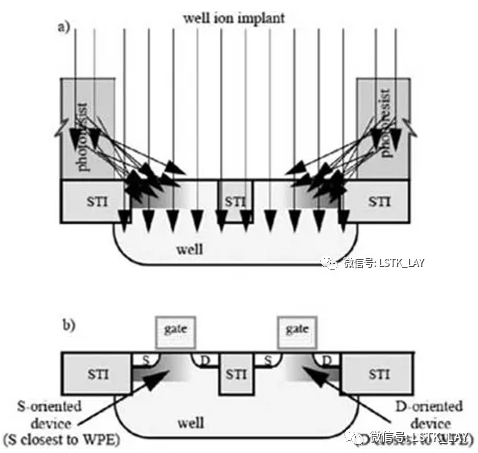

1.2 形成原因

在进行阱离子注入工艺时,离子在光刻胶边界和侧面上发生散射和反射,这些离子会进入到硅的表面,从而影响阱边界附近区域的掺杂浓度。阱边界附近的掺杂浓度是不均匀的,它会随着距离阱边界的远近而变化,距离阱边界越近的区域,浓度越大。也正因为这种不均匀造成mos管阀值电压Vt和饱和电流Id的不同。下图是WPE效应示意图:

1.3 对mos管造成的影响

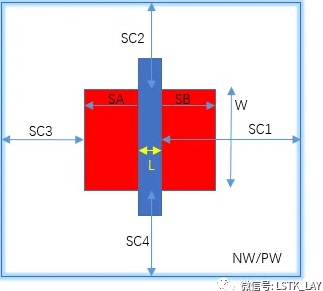

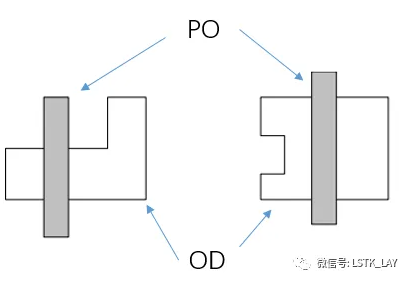

首先定义mos管的几个尺寸表示,如下图:

Tips:这些尺寸表示会陆陆续续在后续文章中出现,请记住这些字母代表的尺寸。

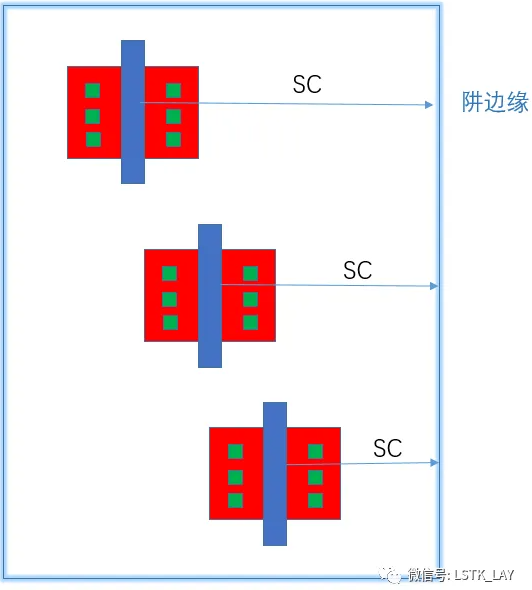

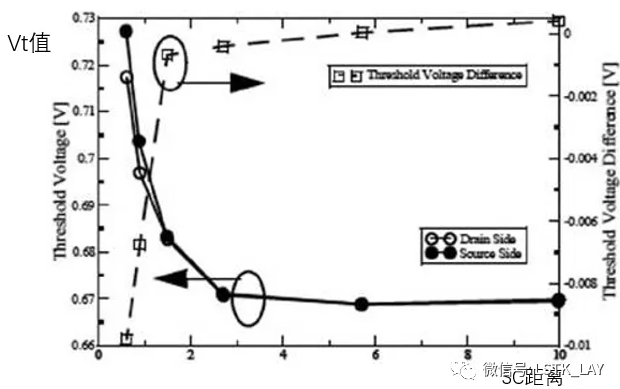

对于相同W、L、SA、SB的mos来说,当SC变化时,阀值电压Vt和SC距离有如下关系:

可以看出SC距离越远时,Vt值的变化越小,到了一定值时(不同工艺有不同距离要求),Vt值基本保持不变。

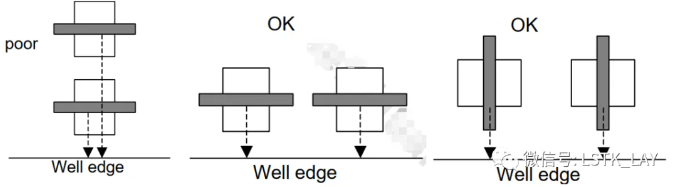

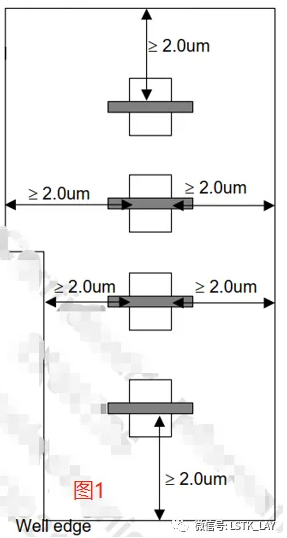

1.4 版图中减小WPE影响的几种方法

1.4.1 优化减少阱个数,如:同一电位的器件放在一个阱里面;

1.4.2 对于一些关键匹配的器件(如差分对、电流镜等),远离阱放置,特别注意在远离的同时,需要注意匹配器件SC值的控制,如下图;如让Vt变化更小,建议SC1、SC2、SC3、SC4大于2um(TSMC 40nm工艺要求)。不同工艺要求不同,具体请参考对应工艺规格书。

1.4.3 在有限的空间内,添加Dummy器件,这样可以使器件远离阱边缘,即增大SC距离值;

Tips:不仅仅阱(NW/PW)影响WPE效应,而且OD2(高压部分,tsmc中名称叫:OD2)也会影响WPE效应。解释如下:

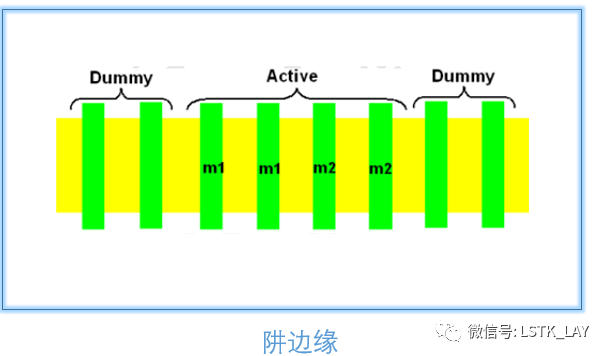

2. PSE效应

2.1 PSE(Poly Space Effect)

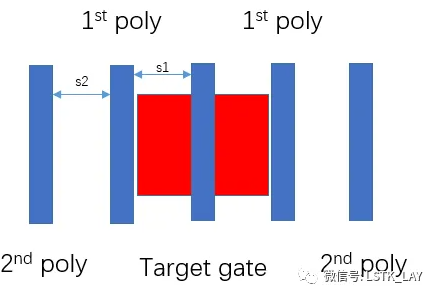

器件Poly与附近Poly间距的不同,对器件性能产生影响的一种效应。示意图如下;

对target gate poly影响的大小:1st poly影响大于2nd poly。一般情况下2nd poly之外的poly对器件本身影响就会很小,通常忽略不计。

2.2 PSE效应对mos影响

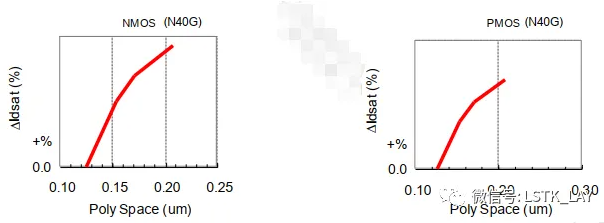

由下图可以明显看出poly间距的不同对应mos管漏电流的影响。(TSMC 40nm工艺,其他工艺请参考规格书)

2.3 版图中减小PSE效应的几种方法

- 根据相关规格书的描述,控制s1和s2距离满足规格书要求;

- 增加dummy PO,一般利用工艺自带撒dummy的rule来添加;满足PO密度要求的同时,也可以减小PSE效应的影响。

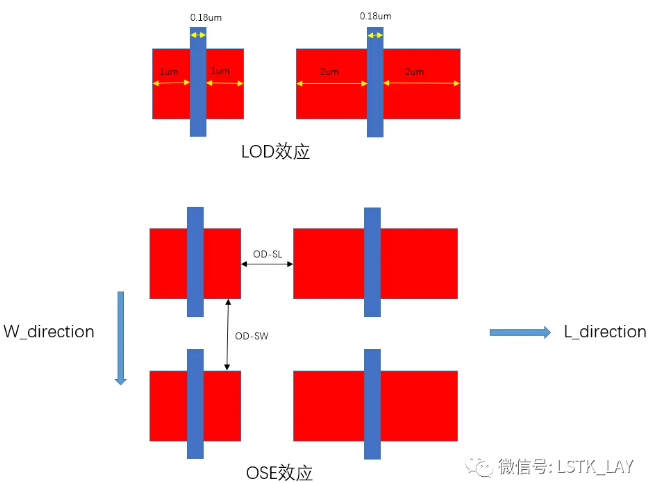

3. LOD效应(STI应力效应)

3.1 LOD效应 (Length of Diffusion effet)

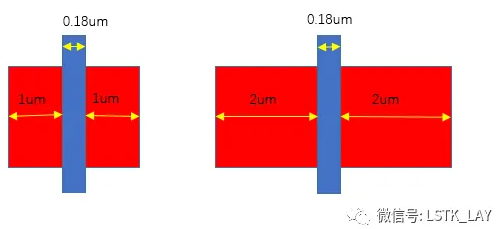

当两个mos有相同的W和L时,由于有源区长度的不同造成一些电气参数的不同,所产生的效应称为LOD效应。

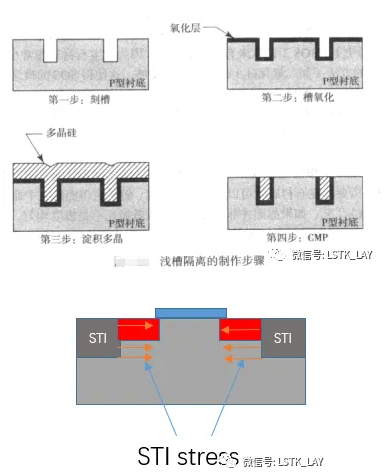

3.2 LOD效应产生的根本原因

在IC制造过程中,为了实现各个有源区的隔离,保证器件之间的正常工作,在较为先进的工艺中采用STI隔离(Shallow Trench Isolation),在STI制造的过程中,其沟槽中填充的是隔离介质氧化物,由于硅衬底和隔离介质氧化物的热力膨胀系数不同,导致 STI会产生压应力挤压邻近MOS 晶体管的有源区和沟道,引起器件的电参数发生变化,这种效应即为LOD效应,也称为 STI 应力效应,LOD 效应主要影响器件的饱和电流 (I)和阀值(Vt)。

3.3 LOD效应应力大小

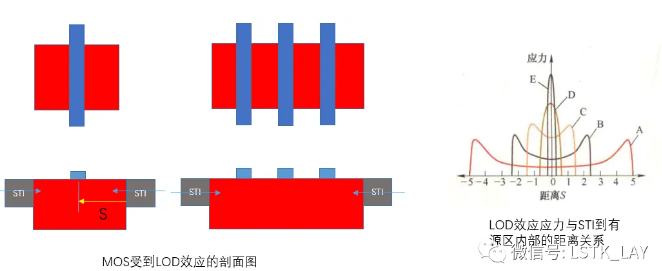

不同长度的有源区,对应受到STI的应力大小不同,从下图可以很明显看出,越往器件中心受到的应力就越小。

S代表:STI边缘到有源区中心的距离。

3.4 LOD效应对mos管的影响

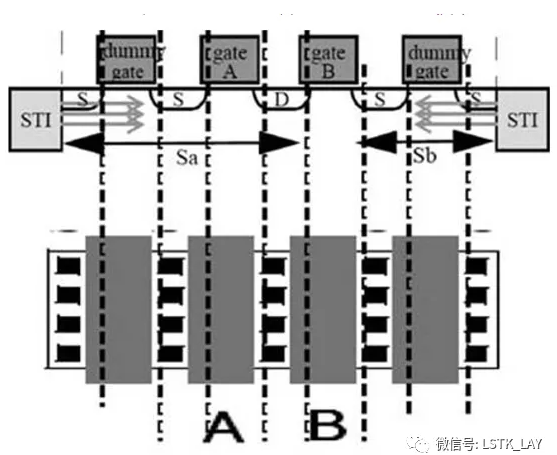

3.4.1 下图展示了版图中mos管的LOD效应示意图,可以看出由于sa和sb值的不同,导致STI产生的应力对mos管B造成的电气性能不同;同理对mos管A也造成影响。

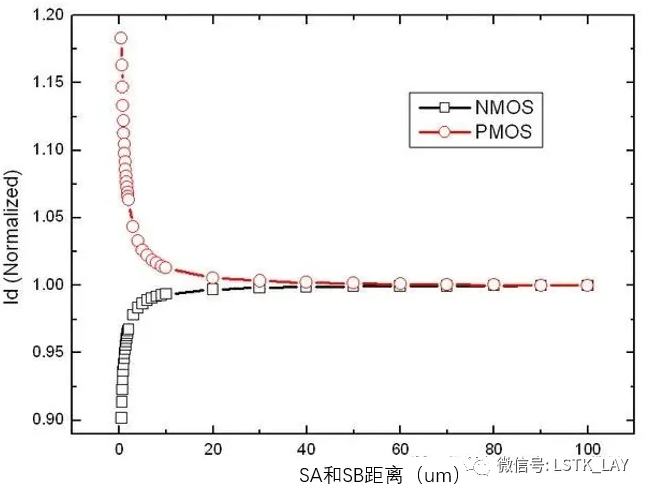

3.4.2 下图展示了LOD效应对PMOS和NMOS管的漏电流的影响,从下图可以看出应力对应PMOS和NMOS管的影响正好相反;

NMOS管:漏电流随SA(SB)的增大而增大;也可理解为,NMOS管的速度会随着应力的增大而减小;

PMOS管:漏电流随SA(SB)的增大而减小;也可理解为,PMOS管的速度会随着应力的增大而增大;

3.5 减小LOD效应的方法

3.5.1 增加dummy器件,使相关mos管受到的应力最小;

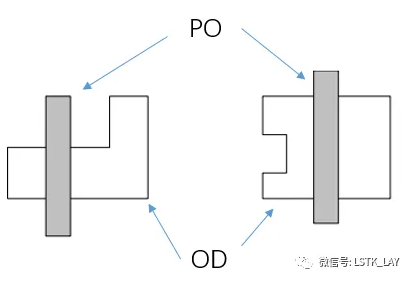

3.5.2 避免不规则的OD形状;

4. OSE效应

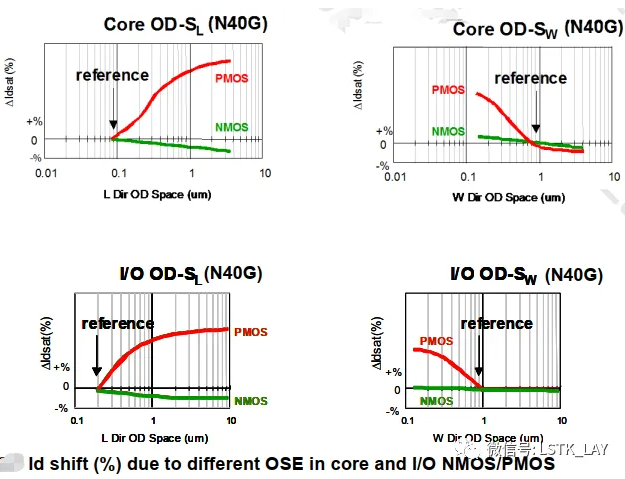

4.1 OSE(OD Space Effect) (TSMC工艺中有源区图层叫OD)

与LOD效应类似,OSE效应也是由于STI应力导致器件电气参数的改变。两者不同的点在于,LOD效应指单个器件本身有源区长度不同导致的影响;而OSE效应指不同器件有源区之间由于STI存在导致器件电气参数的改变。

OSE效应形成的原因这里就不重复描述了,请参考LOD效应产生的根本原因。

4.2 OSE效应对mos管的影响

由下图可以看出OSE效应对应mos管漏电流的影响。(TSMC 40nm工艺,其他工艺请参考规格书)

4.3 版图中减小OSE效应的几种方法

4.3.1 参考对应工艺规格中的描述,控制OD-SL和OD-SW的值,如上图所示;

4.3.2 增加dummy OD,一般利用工艺自带撒dummy的rule来添加,满足OD密度要求的同时,也可以减小OSE效应的影响;

4.3.3 避免不规则的OD形状,不管是在OD-SL或OD-SW方向上;

-END-

*文中部分图片源自网络,侵权删!

参考资料:

【1】The Art of Analog Layout ,Second Edition——Alan Hastings

【2】集成电路制造工艺与工程应用_温德通