本文以理论和实际仿真验证结合的方式,来探讨分析在PDN设计中,电容位置对阻抗的影响。

—-电容的全局特性和本地特性:

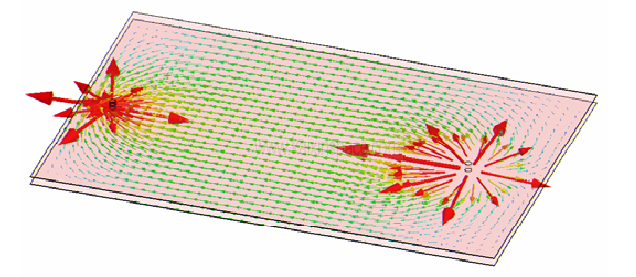

1. 对于电源-地平面对中没有去耦电容的情况(只有平面形成的电容),端口附近的电流会分布到整个平面上以减少回路阻抗。至少在相当高的频率范围内,电流分布到整个平面。然而有源器件均共用此平面的PDN,所以在此时电源-地平面组成的电容,表现出全局特性。

2. 对于电源-地平面对中存在去耦电容的情况,尤其是对于那些高速的去耦电容器来说,它们在低频和高频时会表现出不同的特性,在低频范围内,IC端口的电流会分散到整个PDN平面上,此时去耦电容表现出全局特性,即:电容的位置显得不那么重要;然而在高频范围内,在IC电源端口附近的去耦电容需要给IC提供及时的电流补充,此时电流不会扩散到整个平面,而是在本地形成电流回路,此时可以明显看出去耦电容表现出本地特性,当随着频率增加,去耦电容会表现出强烈的本地特性。即此时电容位置很重要。

—- 从PDN平面寄生电感和电容安装电感角度解释:

当电容的安装电感远远大于PDN中的扩散电感(有电源地平面对之间产生的电感),此时电容的位置不重要;当电容的安装电感远远小于PDN中的扩散电感时,此时电容的位置非常重要;当电容安装电感和扩散电感数量级相当时,此时则需要通过仿真的手段来决定电容的位置对阻抗的影响。(感觉不太好理解,但又没找到好的解释,这里读者可以仔细思考下)

—–当PDN平面和去耦电容表现出本地特性和全局特性需要注意的地方:

当表现全局特性时,所有的电源端口互相影响,彼此产生影响从而使阻抗增加,此时需要使用自阻抗和互阻抗来分析和设计平面PDN。然而,当表现出本地特时,各个电源地端口之间的影响甚微,甚至完全互不影响,可以采用端口自阻抗来分析和设计平面 PDN 。

下面设计案例仿真验证,影响电容位置的几个因素,它们之间的关系:

- 电容安装电感;

- PDN平面扩散电感;

- 频率高低;

设计3个pcb板分别命名为:a板、b板、c板,它们都是4层板,叠构为:Top—GND—PWR—Bottom;铜厚都是1oz;介电常数都是4.5;损耗正切值都是0.02;但不同的是GND和PWR平面对之间间距不同:a板3mil、b板20mil、c板50mil,而PDN平面对中对应的扩散电感从小到大排序为:a<b<c。

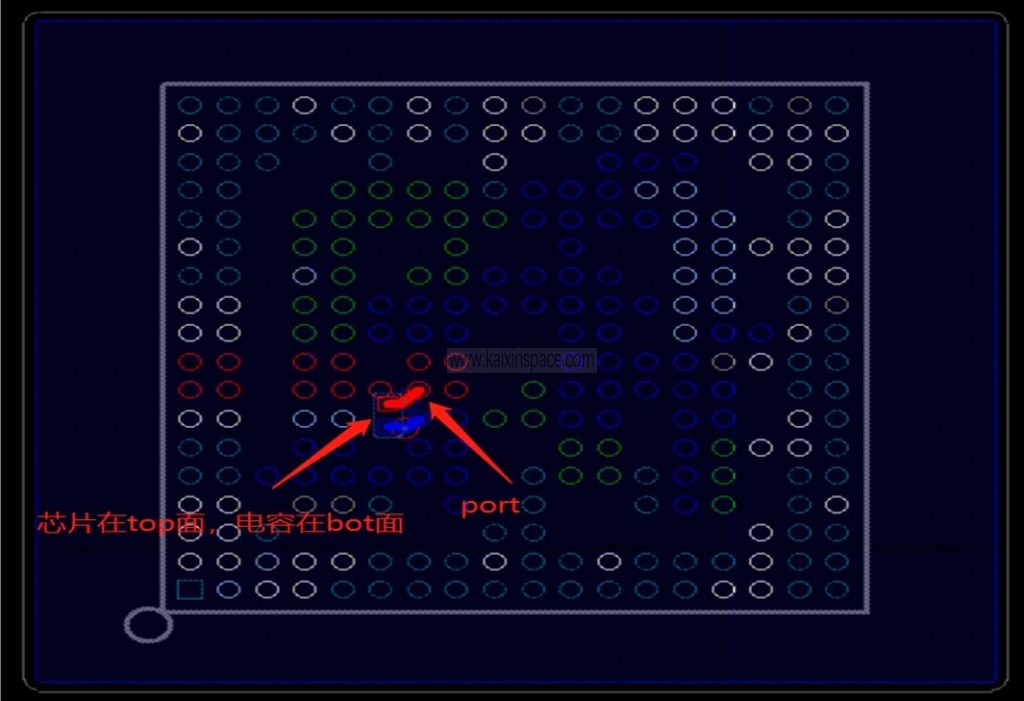

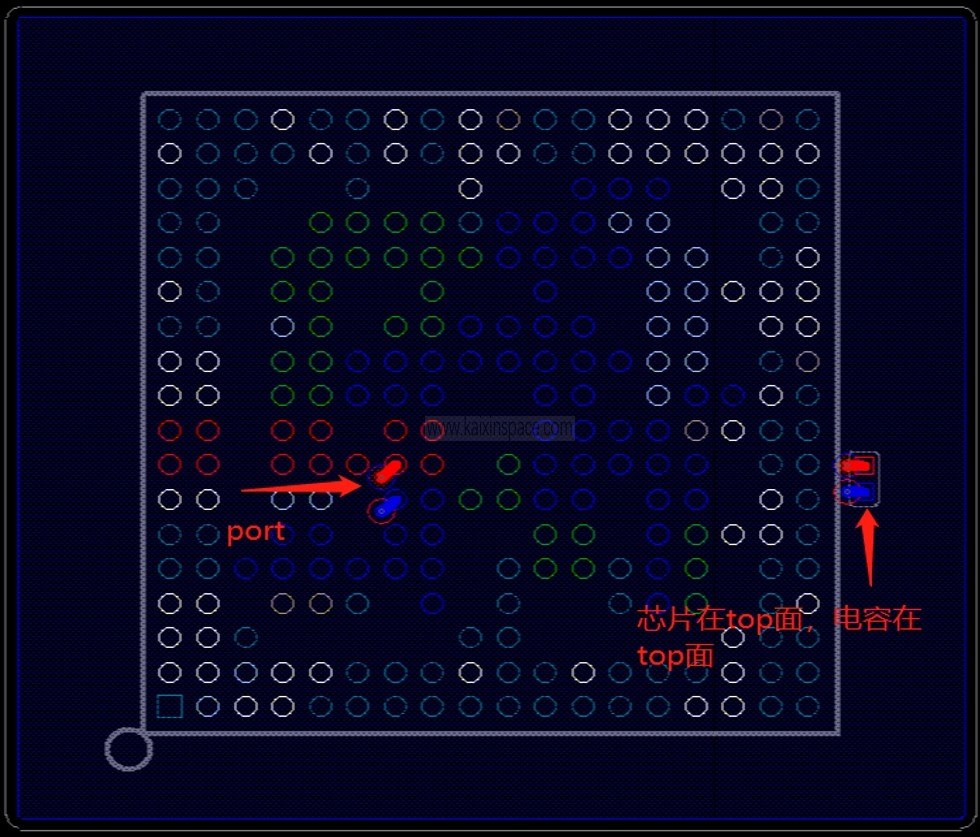

对应的电容位置如下图所示:

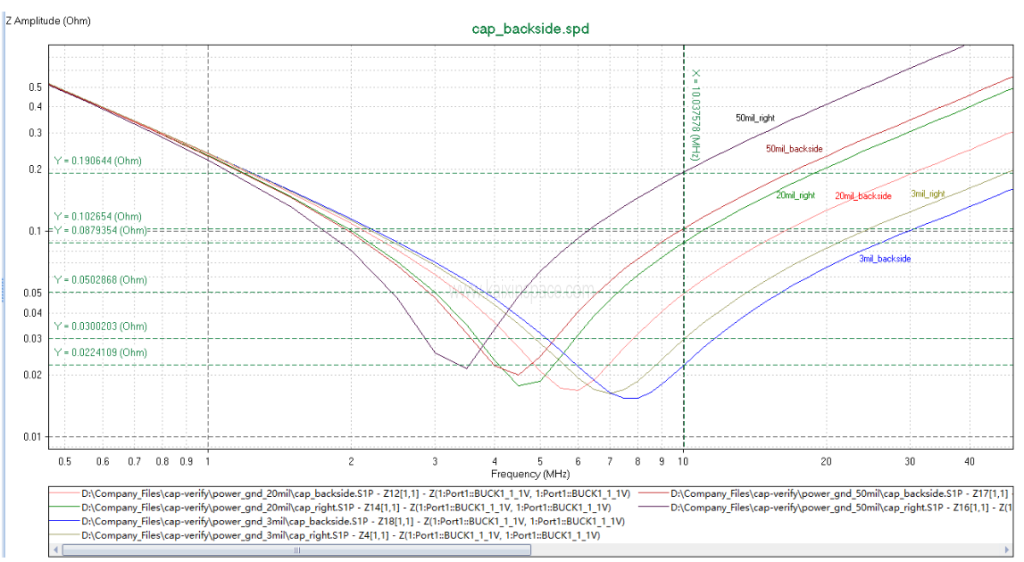

对应3个pcb板仿真的阻抗曲线,如下图所示:

从上图曲线,可看出:

1. 在扩散电感较小时,不同电容位置的影响很小,此时电容位置不是很重要(全局特性);当扩散电感较大时,不同电容位置影响很大,此时电容位置很重要(本地特性)。相同频率下对比:

- 3mil介质厚度的情况下,bot和right位置的电容阻抗值相差很小大概8mohm左右;

- 20mil介质厚度的情况下,bot和right位置的电容阻抗值相差较大,大概40mohm左右;

- 50mil介质厚度的情况下,bot和right位置的电容阻抗值相差很大,大概90mohm左右;

2. 在低频段,在相同电源地平面对间距情况下,从图中可以看出不同电容位置的阻抗相差很小,此时电容表现出全局特性。

3. 随着寄生电感值加大,谐振点不断左移,去耦电容效果变差。

参考:

【1】信号完整性与电源完整性分析(第二版)—【美】Eric Bogatin著,李玉山等译;

【2】高速电路电源分配网络设计与电源完整性分析—张木水

-END-