本文始于2024年12月,以Virtuoso Abstract Generator Version IC6.1.8 结合T家工艺,详细讲解提取LEF文件中常见的三大步骤(Pin Step、Extract Step、Abstract Step),并在文中以抽取”Block”类型的LEF文件为案例,演示其相关步骤。又在其中穿插讲解各个Step的主要功能和注意事项。其他工艺或抽取其他类型的LEF文件,亦可以参考本文。

LEF文件分为:”technology” LEF 和 “Cell library” LEF(IP LEF),前者由Fab提供;后者由Users自己生成。而本文所关注的是后者。

1.1 直接打开(方法1)

1.2 通过GDS导入方式打开(方法2)

1.3 方法1与方法2带来的区别

1.4 小结

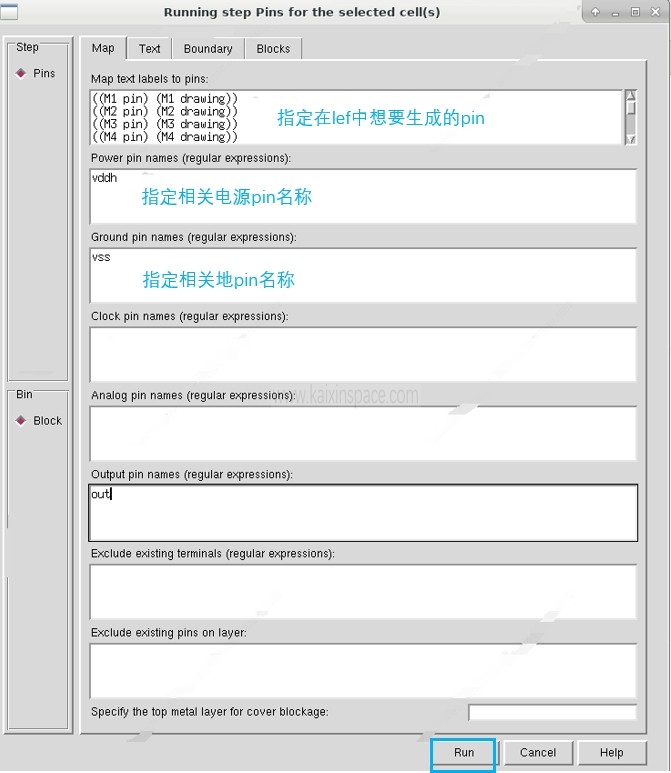

2.1 Map选项

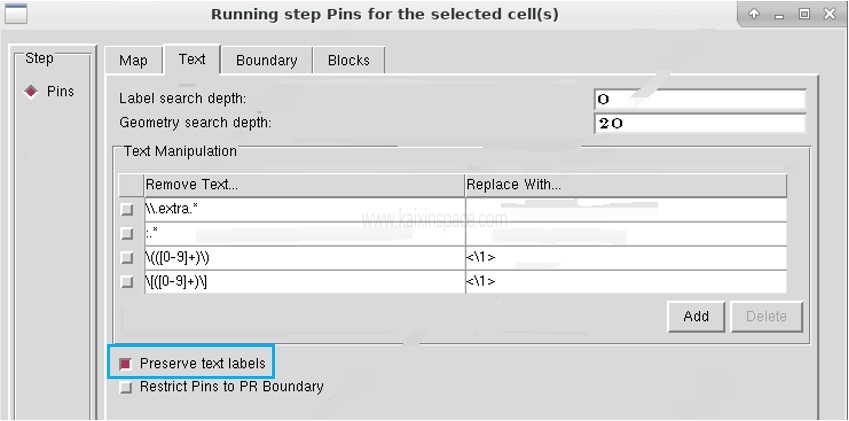

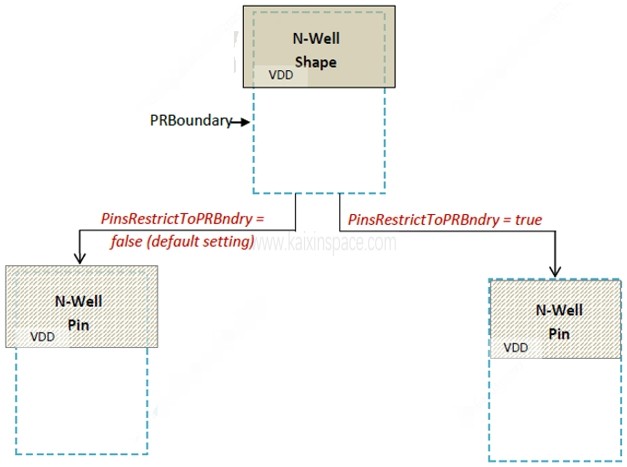

2.2 Text选项

2.3 Boundary选项

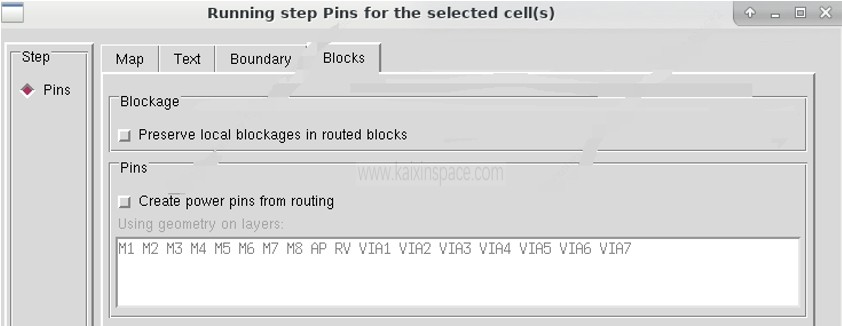

2.4 Blocks选项

3.1 Signal选项

3.2 Power 选项

3.3 Antenna 选项

3.4 General选项

4.1 Adjust选项

4.2 Blockage选项

4.3 Density选项

4.4 Fracture选项

4.5 Site选项

4.6 Overlap选项

5. 问题与讨论

5.3 执行完Extract Step 出现错误信息时,如何解决?

5.4 执行完Abstract Step 出现警告信息,如何解决?

5.5 相同的pin在抽取Antenna数据时,为什么会出现不同的Antenna数据?

5.6 Abstract软件Bin栏中的”Core”、 “IO” 、”Corner”和”Block”都有什么区别?

5.7 Abstract如何将版图中(任意位置和任意层次)没有Label相连的地方提取成pin?

5.8 在4.2小节中,blockage选项中已经勾选了Corridor此选项,但内部的pin为什么没有生成相关边界通道?

5.9 抽取较大版图的LEF文件时,Abstract抽取模型花费时间太长,有什么设置可以有效减少软件提取的时间?

5.10 使用Abstract软件抽取LEF文件和Cadence Virtuoso在CIW窗口自带的File—Export—LEF导出的方法有什么区别?

6. 参考

正式开始抽取LEF文件前的两点建议:☆

(1)请在抽取的layout中,请加入prBoundary层,从菜单栏Creat-P&R project-P&R Boundary创建;

(2)Layout中需要抽取pin的大小,请使用和线宽相同的尺寸(会影响抽取LEF文件中的某些数值)。

1. Abstract打开版图库的两种方式

1.1 直接打开(方法1)

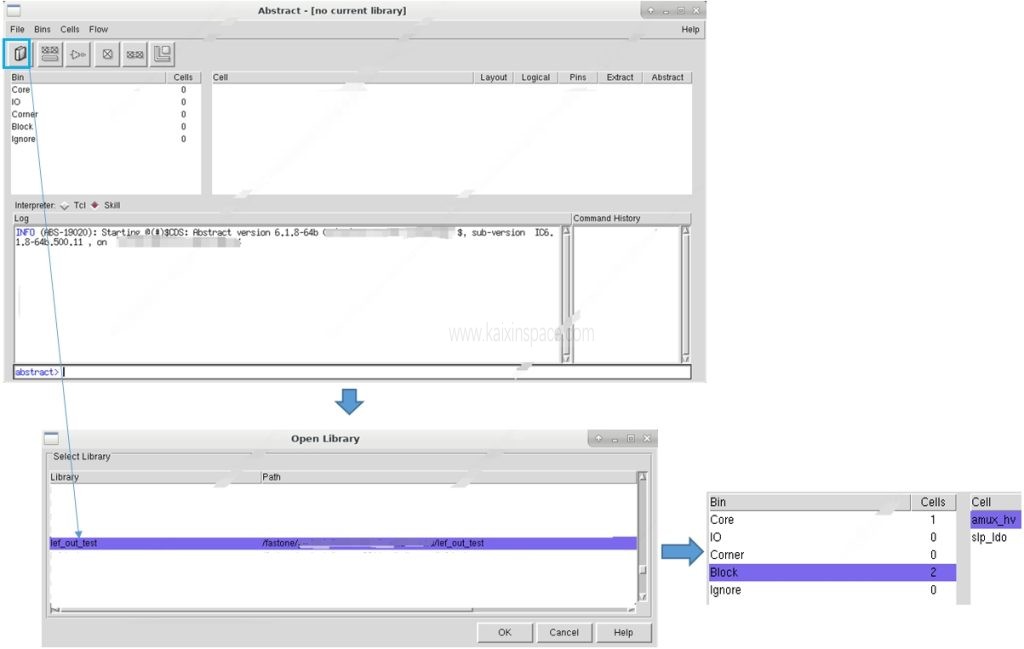

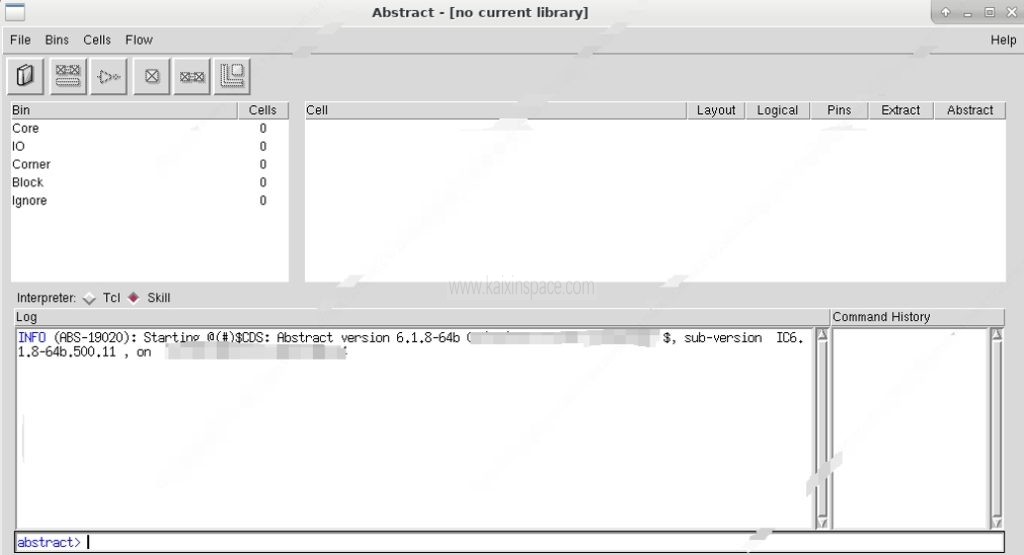

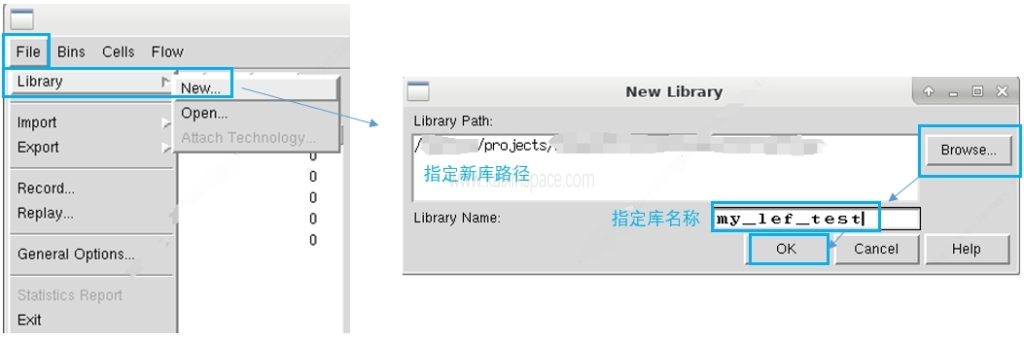

1.11 首先打开Abstract软件,请从启动Virtuoso相同的路径下打开Abstract软件,这样可以共用.cdslib文件,方便查看和管理。然后直接点击“library”按钮(下图蓝框处),对应打开需要抽取LEF的库(建议提前在library manager中新建库,并拷贝需要抽取LEF的版图到此库中,以便和现有库做区分)。

提示:在Bin栏中,默认导入的版图会在Core下,请根据提取需求,选择合适的Bin类型(菜单栏Cells—Move…)。

1.2 通过GDS导入方式打开(方法2)

1.2.1 首先打开Abstract软件,请从启动Virtuoso相同的路径下,打开Abstract软件,这样就可以共用.cdslib文件,方便查看和管理。如下图。

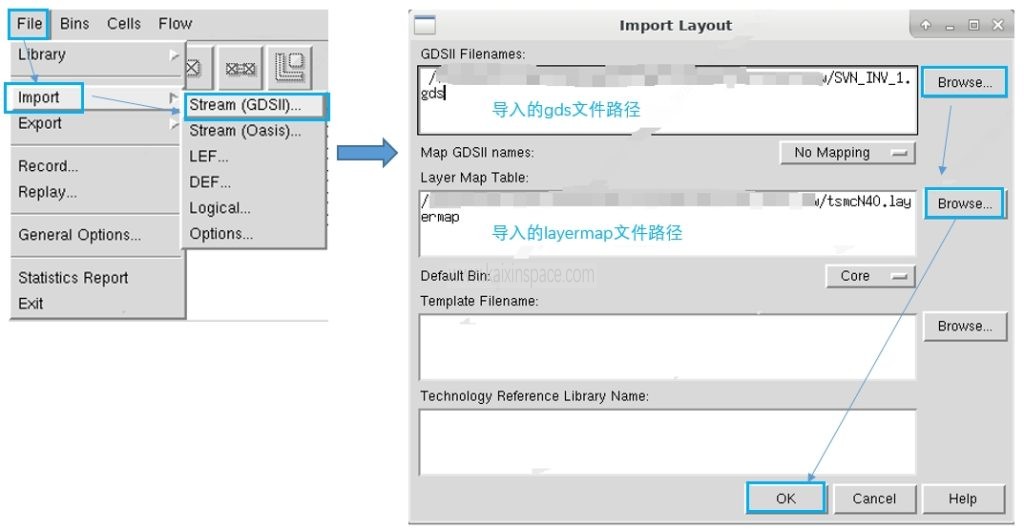

1.2.2 新建一个新的库,并导入相关版图的gds文件和对应工艺的layer.map文件,如下图。

注意:如遇到如下错误,请尝试重新Attach对应工艺的Technology file。

1.3 方法1和方法2带来的区别

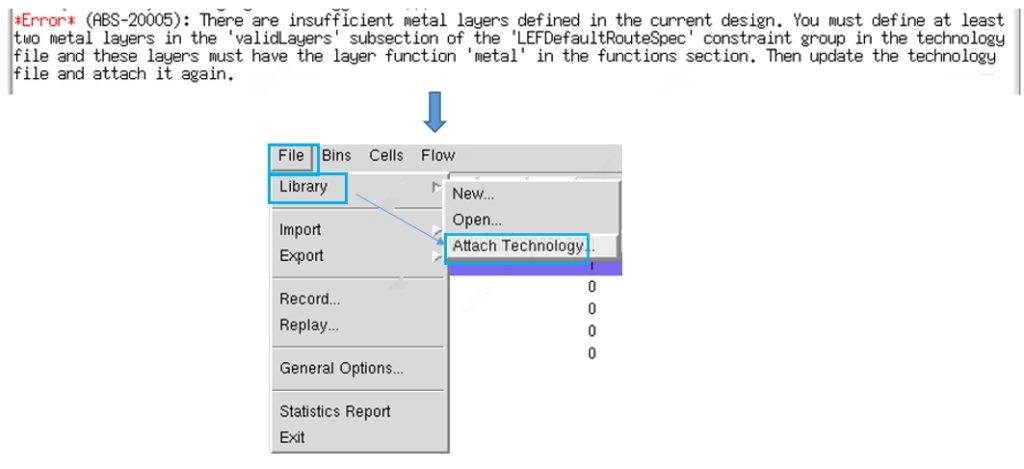

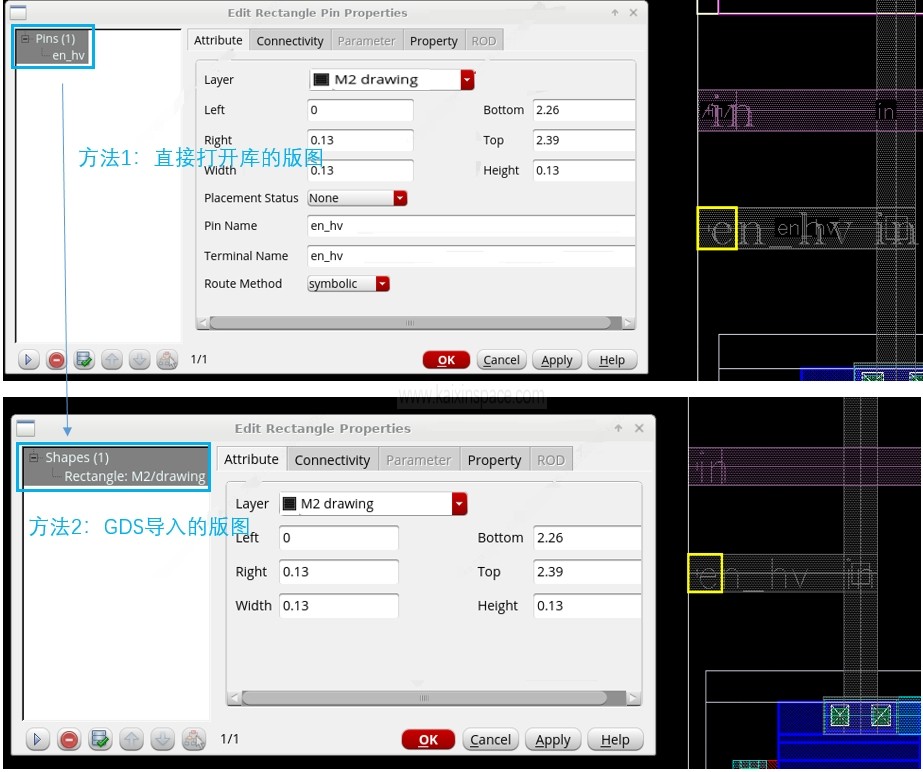

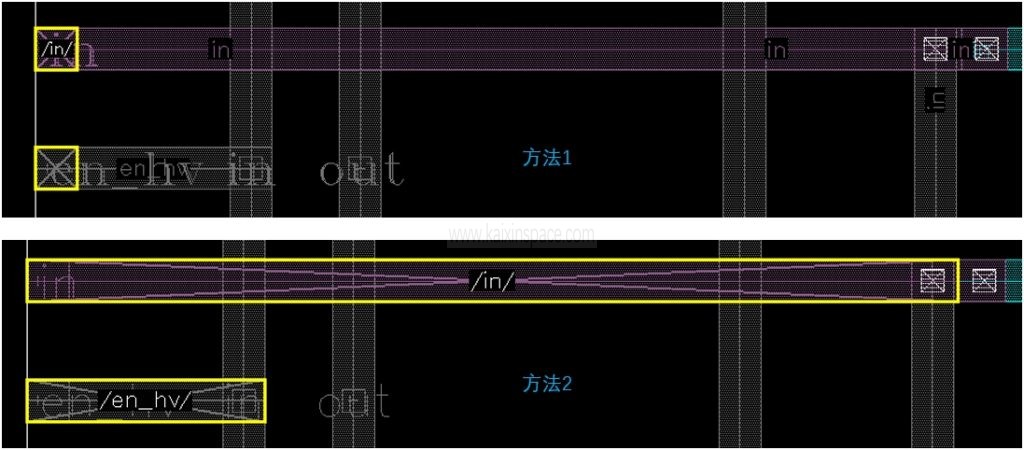

区别1:原版图中pin的属性被更改成shape类型,见下图;

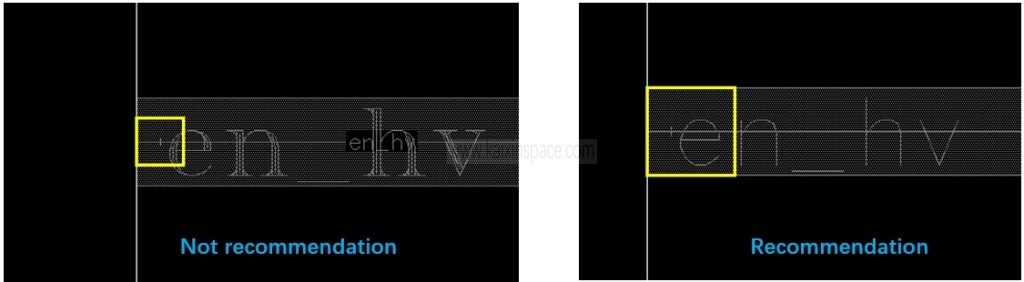

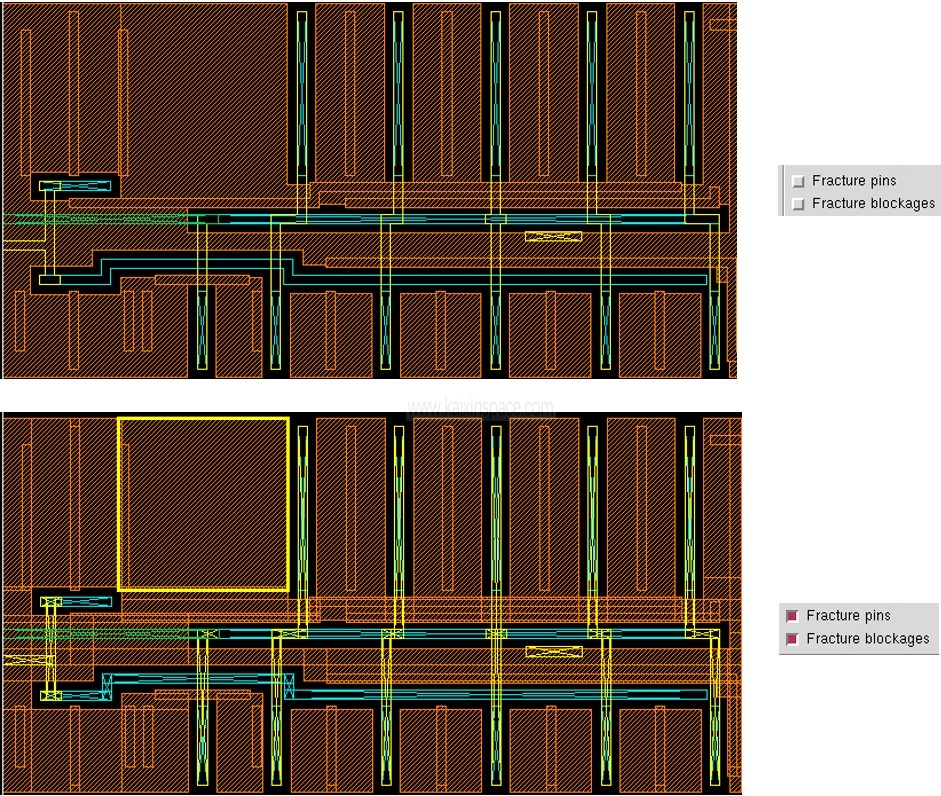

区别2:抽取Bin的类型是Block时,在Pin Step中,方法1,无需指定”Map text labels to pins“栏的值,软件会默认pin的大小,做为实际生成pin的大小;而在方法2中,则需要在”Map text labels to pins“中指定有效语句(请参考下文Pin Step中相关的说明)。并且两个方法生成的pin的大小也会有不同。参考下图,黄色为生成的pin大小。

1.4 小结 ☆

方法1中生成pin大小的原则是:Abstract以terminal中实际pin大小来生成的pin大小;

方法2中生成pin大小的原则是:Abstract将label 下面对应的metal(shape)直接生成pin的大小。

(上述2个原则对signal和power的net均适用)

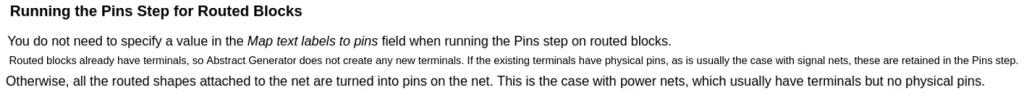

help手册中的一段话:

注意:上述生成的pin大小仅仅是Pin Step中生成pin的大小,最终Abstract生成pin的大小还会和Extract Step 和Abstract Step中的设置相关。☆

此处开始介绍详细流程和步骤;

下文将以Bin类型为Block为例,来抽取LEF文件,并以此来说明相关流程和注意事项。

总的来说抽取LEF文件主要分为3大步,分别为:

(1)Pins的相关设置

(2)Extract相关设置

(3)Abstract相关设置

2. Pin Step相关设置

2.1 Map 选项

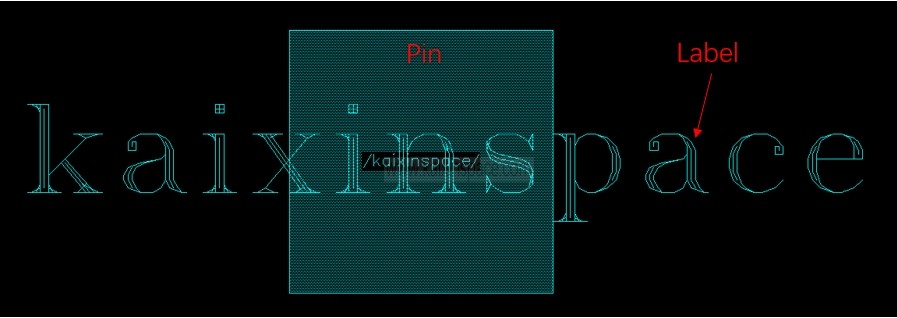

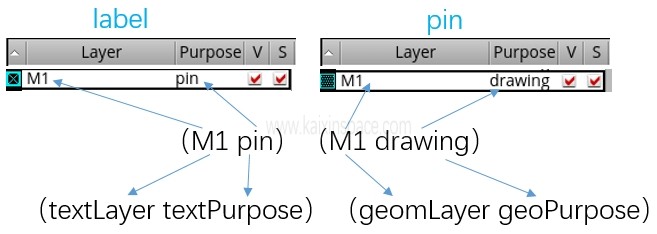

“Map text labels to pins“栏中,请根据正确的语法格式,填写想要抽取的pin信息,其语法格式如下:☆

(textLPP1 geomLPP1 geomLPP2)其中:

textLPP1可以写成:(textLayer textPurpose)或者仅仅是textLayer;

geomLPP1可以写成:(geomLayer geoPurpose)或者仅仅是geomLayer。

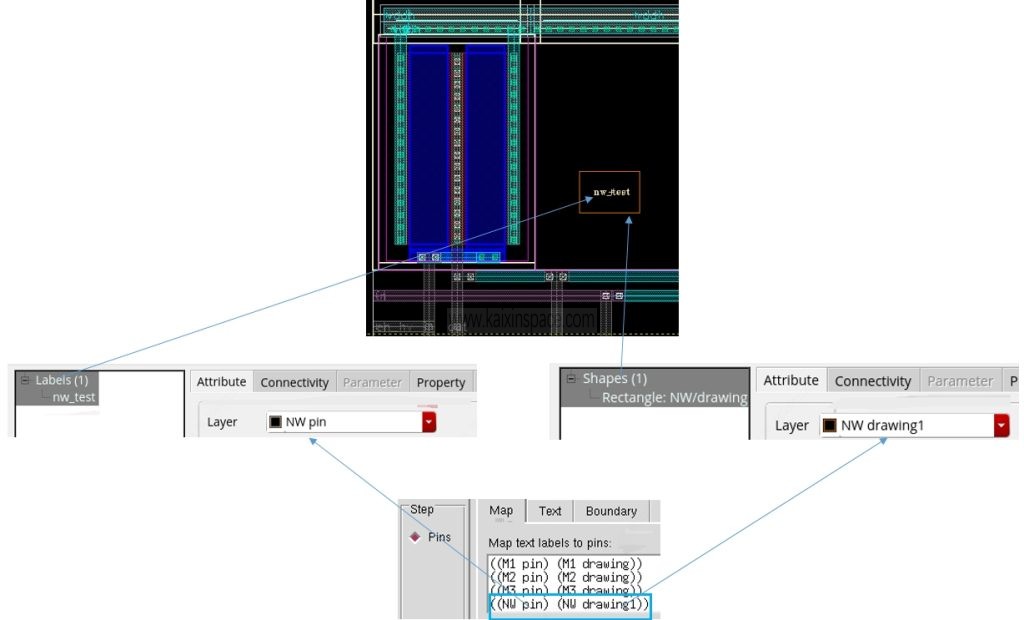

请参考下图解释:

在此例中我们可以写成如下:此语句告诉Abstract Generator要将M1 pin层的labels映射到M1 drawing层上,以便在M1 drawing层上生成对应的物理pin。

((M1 pin)(M1 drawing))

((M2 pin)(M2 drawing))

((M3 pin)(M3 drawing))

((M5 pin)(M5 drawing)) ...注意1:从上述语法格式中可以看出,这里有不同的格式写法,请根据需要书写即可。

注意2:不同工艺所识别的pin和lable,所在的layer purpose存在差异,请注意区分。

当抽取的Bin类型是Block时,并且以上述方法2导入相关库,那么Map选项中的其他设置,见如下图;

其他net类型的pin name 请根据需要进行填入即可。

2.2 Text选项

这里主要设置Label和Geometry搜索层次的深度(0:表示当前层;1:表示次当前层,以此类推。)和设置抽取LEF文件中pin的名称一样,一般我们保持默认即可。相关设置如下图;

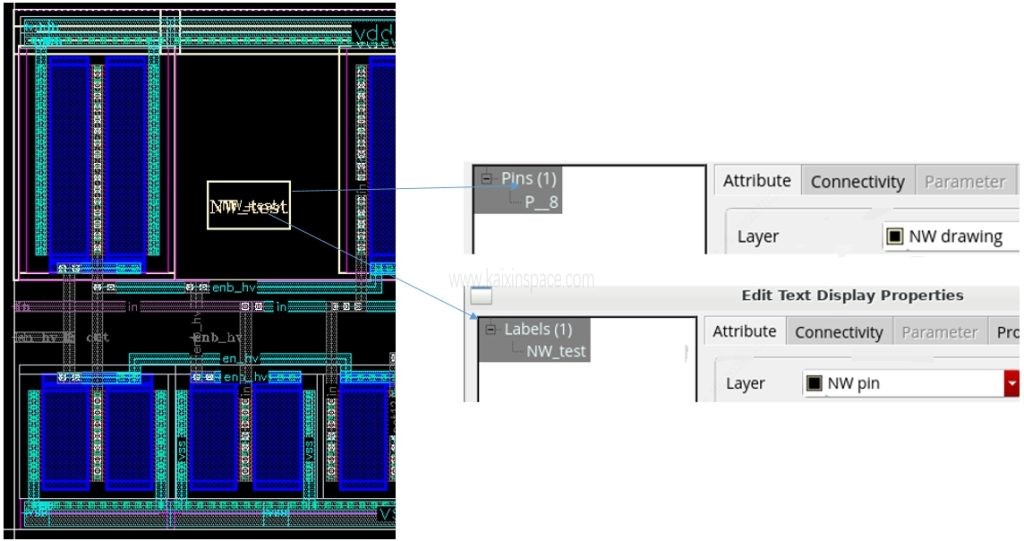

当你想抽取自定义的NW作为pin时,”Restrict Pins to PR Boundary“这个选项可以让你将NW的pin控制在prBoundary以内,请参考下图;

2.3 Boundary选项

这里主要告诉Abstract如何生成prBoundary,此项体现在LEF文件中的SIZE栏,但SIZE中只能指定Rectangular形状,而如果要生成Rectilinear Polygon形状,需要在Abstract Step中对应设置”Overlap”相关参数,点这里查看。

“Create boundary”这里有三个选项,分别解释如下:☆

- “off“:工具不生成prBoundary而直接使用版图中的prBoundary。如果版图中没有prBoundary,工具会报错;

- “as needed”:如果版图里有prBoundary,那么工具就使用这个prBoundary。如果版图里没有,工具会根据”Using geometry on layers“列表里的层次来自动生成;

- “always”:不管版图里是否有prBoundary,工具都会根据”Using geometry on layers“列表里的层次来自动生成prBoundary。

当抽取的Bin类型是Block时,此选项中的相关设置如下图。

2.4 Blocks选项

勾选”Preserve local blockages in routed blocks“,保留已有的blockages信息,典型的是从DEF文件导入到Abstract软件进行抽取;

同样,勾选”Create power pins from routing“,表示容许软件从导入DEF文件中的走线数据创建电源引脚。如果布局中没有明确定义电源引脚,可以通过此功能从走线数据中生成电源引脚,通常是在DEF文件的”SPECIALNETS“部分中定义的。

正常抽取LEF文件时,保持默认即可。如下图:

最后点击Run,可以看到对应的pin下有绿勾出现,至此Pin Step完成。

Pin Step完成后,可以实时查看Abstract对应生成的pin情况;(这里有两种方式)

方式1:在Abstract软件菜单栏点击Cells—Edit—Pins…即可;

方式2:回到Library Manager中,直接打开对应库中生成的abstract.pin的文件即可。

3. Extract Step相关设置

3.1 Signal选项

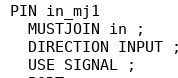

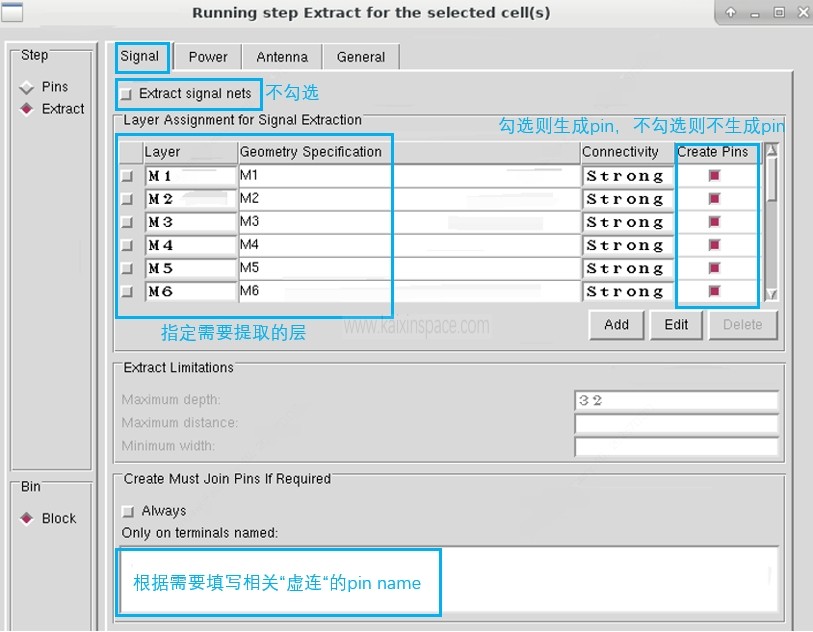

在此选项中,您可以指定Abstract软件想要提取Signal的层、要在哪些层上创建Pin以及设置提取的限制,并且当版图中出现虚连(同一个net,没有物理连接,通过Labels虚连一起)情况时,你还可以使用此选项卡中的”Create Must Join Pins If Required“功能,来产生具有”虚连”属性的LEF文件。

注意:当有使用”Create Must Join Pins If Required“功能时,“Extract signal nets”必须勾选,否则此功能将不起作用。

导出的LEF文件中,将带有”MUSTJOIN”字样,如下图;

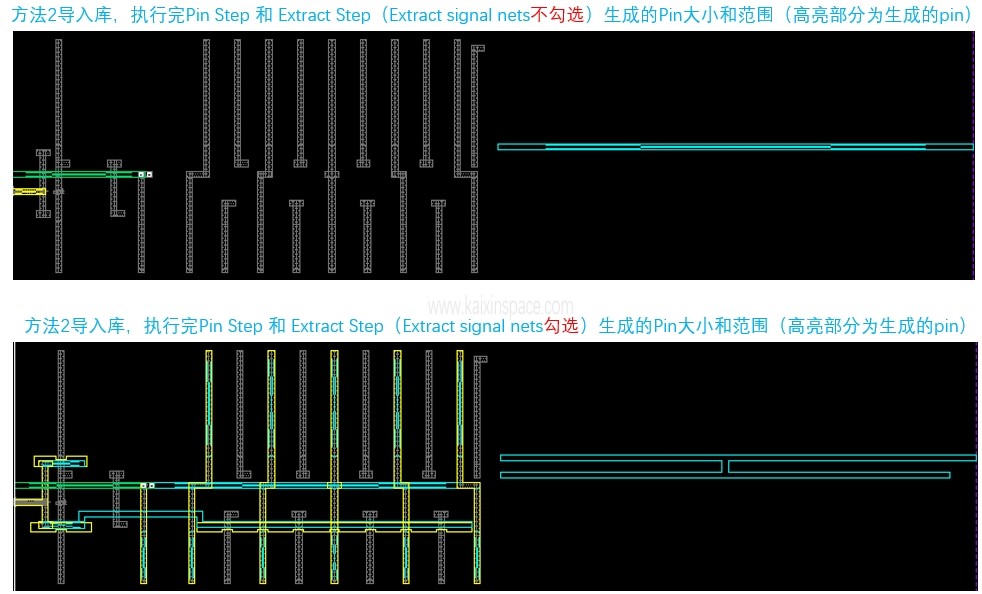

当抽取的Bin类型是Block时,建议“Extract signal nets”不勾选(版图中没有”虚连”的pin存在);

注意:这里的相关设置会影响生成signal pin大小和范围。☆

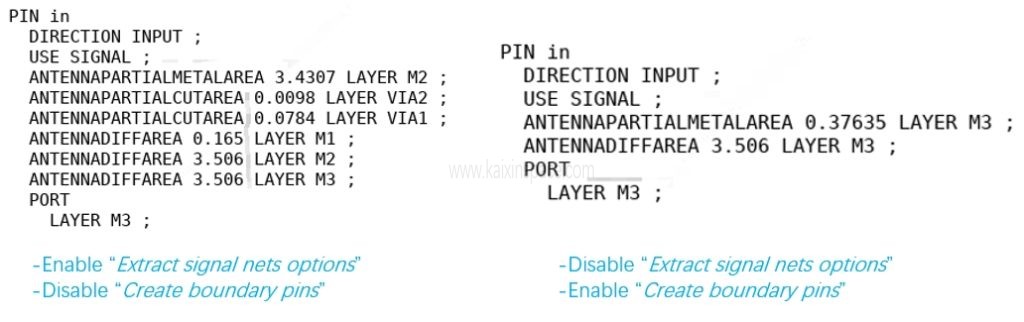

当“Extract signal nets”勾选时,Abstract将”Layer Assignment for Signal Extraction“中的层或过孔转化为pin(当你每层都勾选”Create Pins“时);也就是此设置会覆盖Pin Step 中生成Signal pin的大小和范围。

当“Extract signal nets”不勾选时,Abstract将保持Pin Step中生成的Signal pin的大小和范围。

重重重点来了! ☆

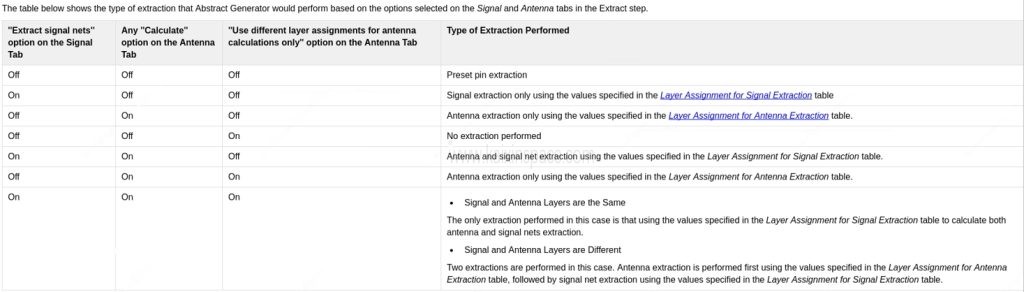

说明Signal Tab 和 Antenna Tab两个选项中存在的关系;它们相互关联并且影响整体提取数据;

下表旨在让Users理解Abstract在进行抽取Signal或者Antenna相关的数据时,它是通过哪些分配层数来进行抽取。

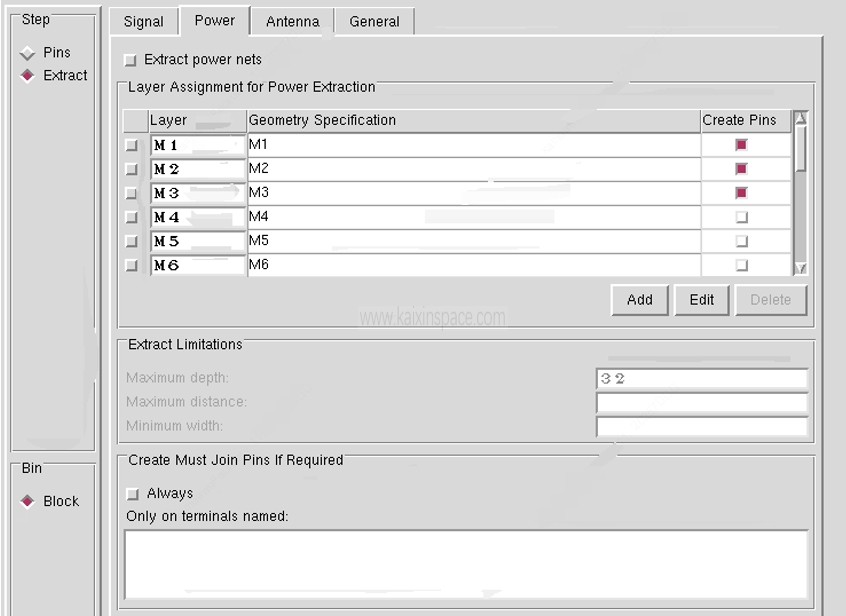

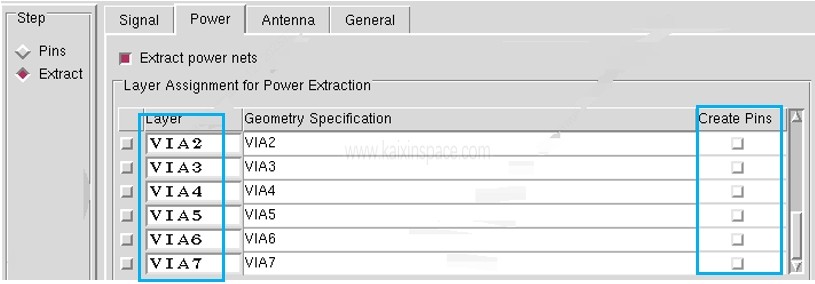

3.2 Power 选项

这里请直接参考Signal选项中的相关解释。

当抽取的Bin类型是Block时,“Extract power nets”可根据抽取的需要来勾选或者不勾选。如果你在Pin Step步骤中,已抽取了想要形状的Power pin,那么这里可以不勾选;反之,如果在Pin Step中,没有得到想要形状的Power pin,那么请勾选此选项。

另外,请根据需要,适当的对”Creat Pins” 进行设置;(对版图中power net的走线层中,设置哪些层需要生成pin,哪些层不需要生成pin)

注意:这里的相关设置同样会影响生成power pin大小和范围。☆

当“Extract power nets”勾选时,Abstract将”Layer Assignment for Power Extraction“中的层或过孔转化为pin(当你每层都勾选”Create Pins“时);也就是此设置会覆盖Pin Step 中生成power pin的大小和范围。

当“Extract power nets”不勾选时,Abstract将保持Pin Step中生成的power pin的大小和范围。

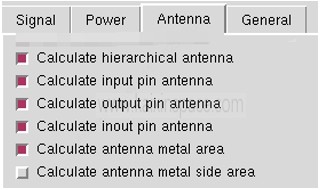

3.3 Antenna 选项

在此选项中,你可以让Abstract提取相关的Antenna信息;如果你需要提取,请打开相关设置。

然而在进行此步骤设置之前,站长强烈建议先学习本站相关文章,点这里。☆

进行Antenna的抽取前的相关设置;

(1)选择需要对应计算Antenna的选项,如下图;

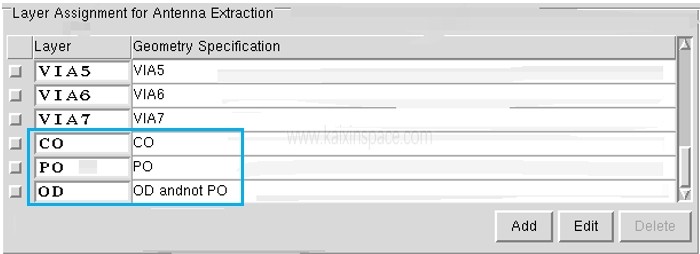

(2)根据对应pdk中对有源区和栅氧区的描述,在”Layer Assignment for Antenna Regions“设置正确Antenna Regions;一般无需更改,默认Abstract软件会自动读取techfile中的相关信息;

(3)在”Layer Assignment for Antenna Extraction“中增加接触孔(CO)、栅级(PO)、有源区(OD)这三个层次,因为在计算Antenna时,需要用到这些层的数据。

(4)最后选中”Use different layer assignments for antenna calculations only“选项,以确保抽取antenna的数据是使用”Layer Assignment for Antenna Extraction“下的设置。可参考此处表格。

当抽取的Bin类型是Block时,Antenna选项中相关设置如下图所示:

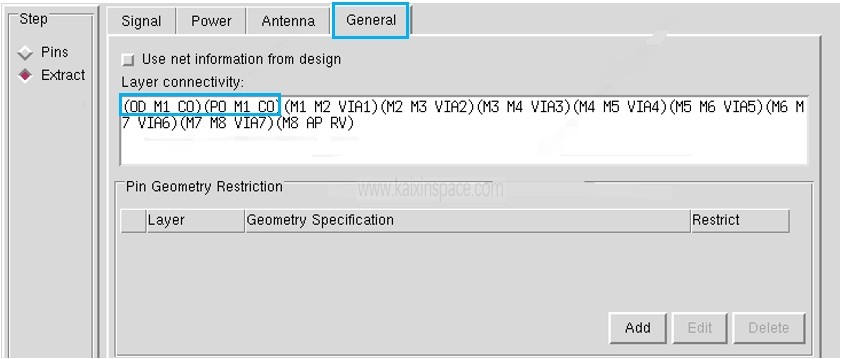

3.4 General选项

在此选项中,检查每层金属的上下层连接关系是否都在列表中(格式:(M1 M2 VIA1)),并增加如下蓝色框中的内容。以确保提取Antenna数据的完整性。

最后点击Run,可以看到对应的Extract下有绿勾出现,至此Extract Step完成。

Extract Step完成后,可以实时查看extract生成pin的情况;(这里有两种方式)

方式1:在Abstract软件菜单栏点击Cells—Edit—Extract…即可;

方式2:回到Library Manager中,直接打开对应库中生成的abstract.ext的文件即可。

4. Abstract Step相关设置

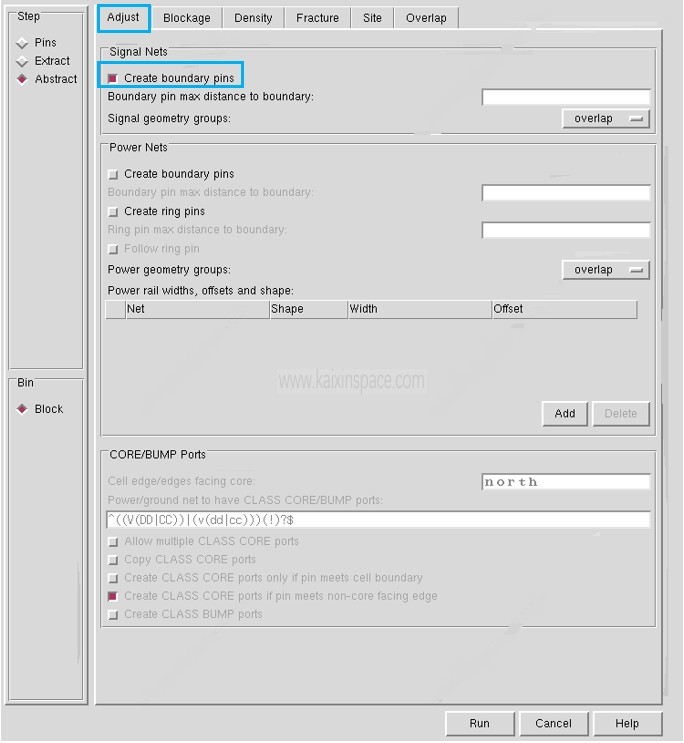

4.1 Adjust选项

在此选项中你可以重新调整在Pin Step和Extract Step中生成Signal和Power pin的大小和形状,也就是说,此步骤的设置,将最终决定你生成pin的大小和形状。

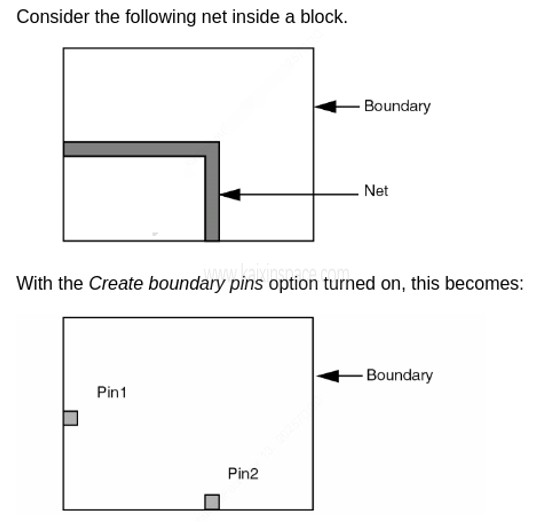

勾选”Create boundary pins“会将提取的pin调整为正方形,并放在Cell的边界处。如下示意图;

Tip1:”Create boundary pins“对Bin类型为”Core”是禁用的,对于其他的Bin类型默认均处于不勾选状态;

如果你想提取Power Nets中的ring pins,那么请勾选”Create ring pins“,并且在Extract Step的Power Tap中的”Extract power nets“也需勾选,以保证abstract能抽取到完整的power ring。

Tip2:Power Nets中的”Create boundary pins“和”Create ring pins“为互斥,只能选择一个,另外”Create ring pins“仅在Bin类型为Block中才起作用;

Tip3:”CORE/BUMP Ports“仅在Bin类型为”IO”时,才有作用。

当抽取的Bin类型是Block时,Adjust选项中相关设置如下图所示:

“Power rail widths,offsets and shape“多用在Bin类型为Core中。

4.2 Blockage选项

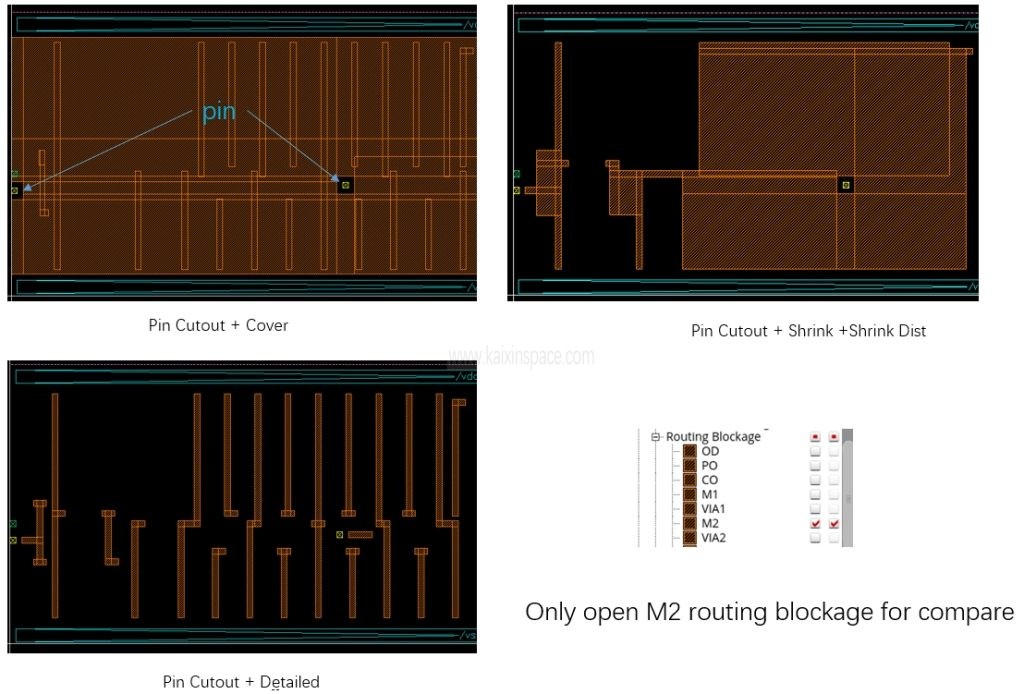

在此选项中,你可以控制Abstract最终生成每层layer的blockage的形状和大小。

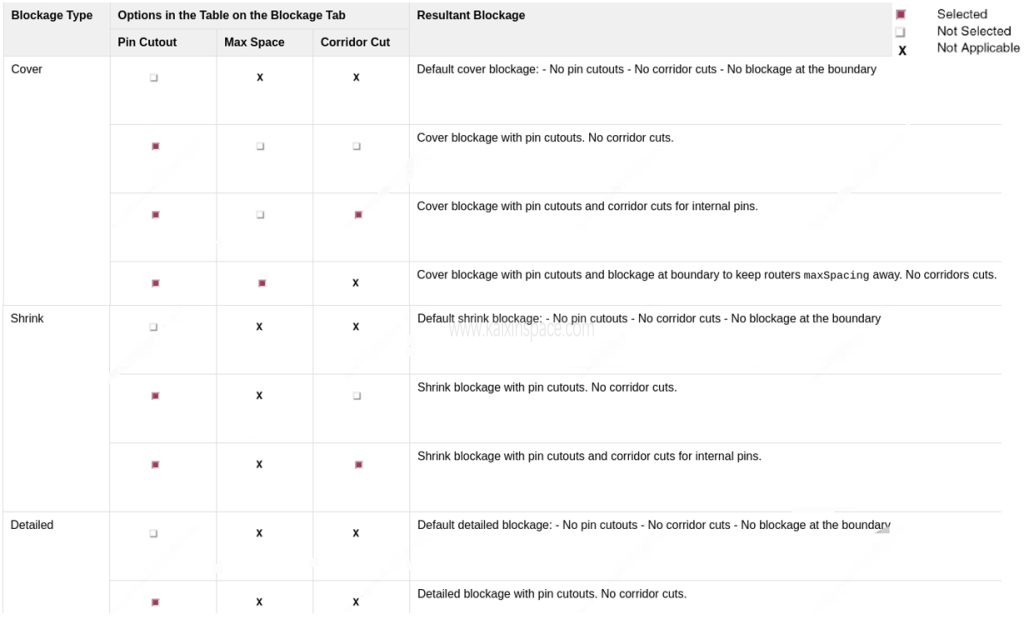

Blockage的类型有三种:

Cover:表示生成的blockage覆盖全部layer;

Detailed:表示仅有走线的地方将被生成blockage;

Shrink:表示生成的blockage的大小和Shrink Dist 与Shrink Tracks有关,一般情况下,在走线密集的地方会根据设定的值,全部生成blockage,而对于没有走线或版图中空白较大的地方,将不生成blockage。

勾选Pin Cutout:表示在生成blockage时,pin的部分将被暴露出来;反之,不勾选则pin的部分将被覆盖。

实际应用中,Pin Cutout将被勾选。

如下是三种blockage类型配合Pin Cutout的图示,请参考;

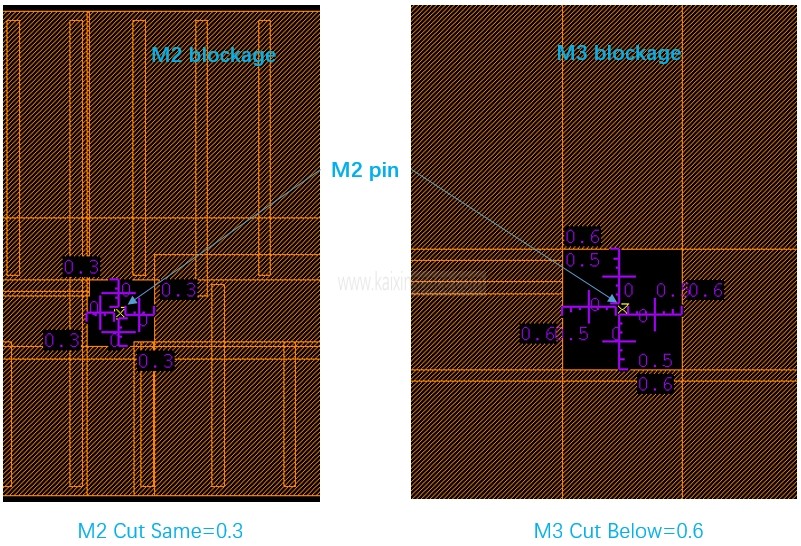

Corridor Cut:表示切开blockage,创建一个通道,使后续连线可以访问到内部pin;请参考下图;

Cut Same:表示根据对应层设定的值,将pin周围blockage切开相应的距离;

Cut Below:表示根据对应层设定的值,将pin位置对应的上下层的blockage切开相应的距离。

请参考下图;

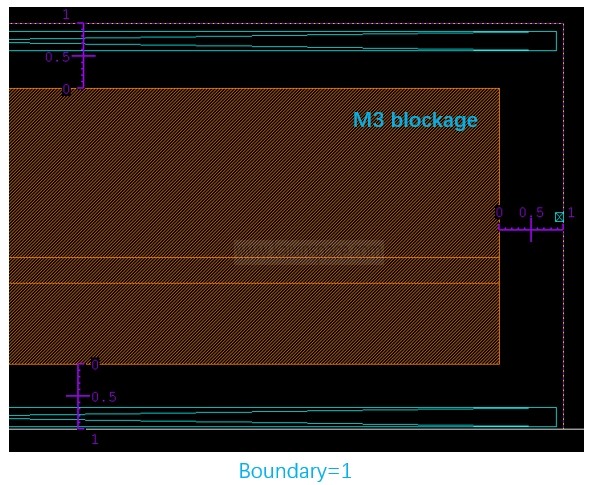

Boundary:表示生成的blockage距离prBoundary边缘的距离;

请注意:Blockage Type与Pin Cutout、Max Space和Corridor Cut,存在组合关系,具体请参考下图。☆

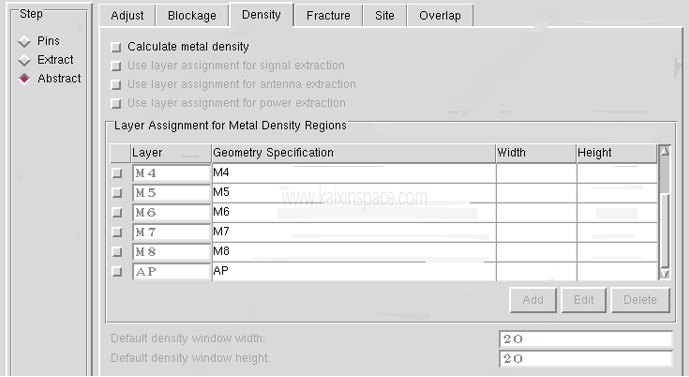

4.3 Density选项

在此设置中,你可以将实际版图中的密度同步到LEF文件中,LEF文件中的信息可以降低内存需求,提高工具的验证速度。

无需设置,默认即可。有需要的Users请参考help。

4.4 Fracture选项

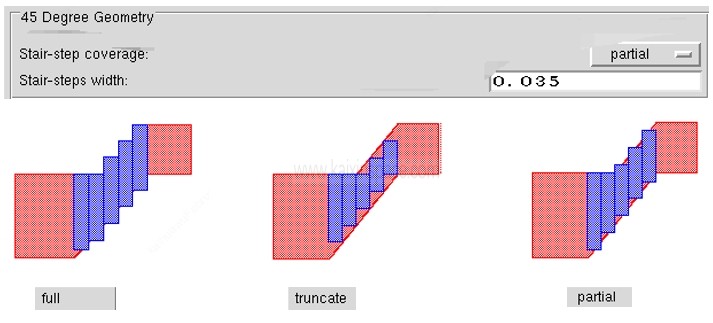

此选项中,你可以控制生成pin和blockage的图形是打散的还是合并在一起的,同时你也可以控制含45度的图形的生成方式(LEF5.8),请参考如下图。

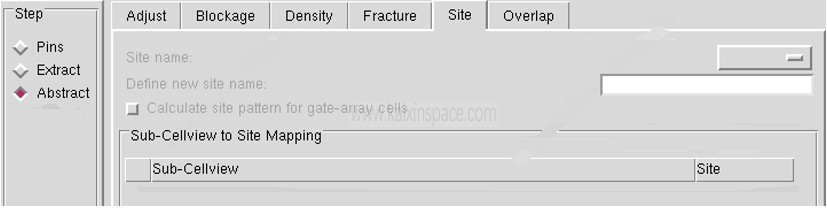

4.5 Site选项

在此选项中,你可以为stdcell自定义一个Site name,以方便后续PR工具可以方便识别它们,来进行相关的布局布线。

Site选项在Bin类型为Block时,被禁用;而在Bin类型为Core时,则必须要有Site name被定义在LEF文件中。

当抽取的Bin类型是Block时,Site选项被禁用,默认即可。

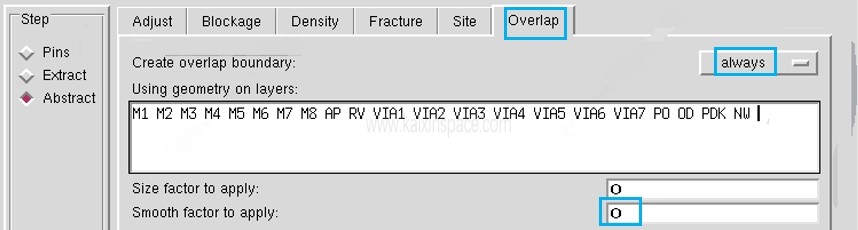

4.6 Overlap选项

此选项中,你可以再次控制prBoundary生成的形状和大小。

让我们先回忆下,第一次生成的Boundary形状是在Pin Step中的Boundary选项中,但Pin Step中的Boundary只能是Rectangular形状,当我们想要生成Rectilinear Polygon形状时,就需要在”Overlap”中进行设置。

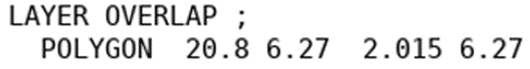

当你成功使用了此功能,那么在你导出LEF文件的结尾会出现“LAYER OVERLAP”字样;

“Create boundary”这里有三种生成方式:☆

- “off”:工具不生成prBoundary而直接使用Pin Step中生成的prBoundary;如果Pin Step也没有生成prBoundary,软件就会报错;

- “as needed”:如果在Pin Step中已经生成了prBoundary,那就使用此prBoundary;如果在Pin Step中也没有生成prBoundary,那么工具就会根据”Using geometry on layers“列表里的层次来自动生成边界;

- “always”:忽略Pin Step中生成的prBoundary,工具会根据”Using geometry on layers“列表里的层次来自动生成边界。

“Size factor to apply“:控制提取LEF缩放比例的一个系数;

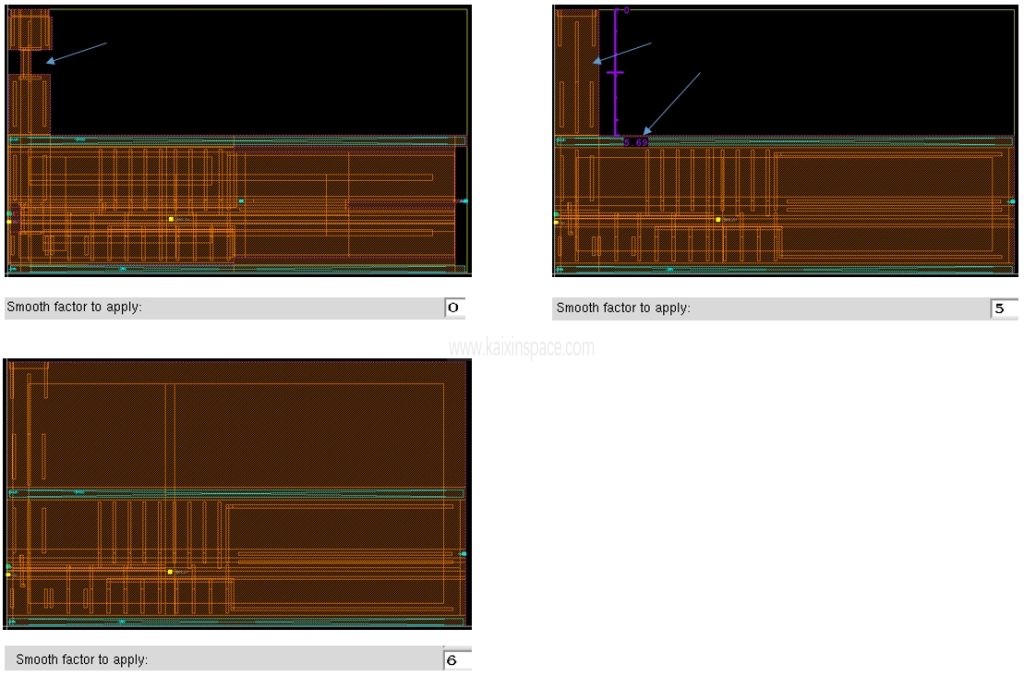

“Smooth factor to apply“:控制提取边界平滑度的参数。也就是它决定了在生成外边界时,是否对原始版图中不规则或角落的边界进行平滑处理。此数值越小就越能保持和原版图边界一样,数值越大则提取的边界就越简化。当设置为0时,表明提取不进行平滑处理,保持和原版图边界形状一致。请参考下图;

注意:当设置”Cteate overlap boundary“为”always“时,生成的prBoundary将由参数”Smooth factor to apply“决定,而与版图中是否绘制prBoundary无关。

当抽取的Bin类型是Block时(多边形边界),请按如下图设置。

最后点击Run,可以看到对应的Abstract下有绿勾出现,至此Abstract Step完成。

Abstract Step完成后,可实时查看最终生成的LEF视图;(这里有两种方式)

方式1:在Abstract软件菜单栏点击Cells—Edit—Abstract…即可;

方式2:回到Library Manager中,直接打开对应库中生成的abstract的文件即可。

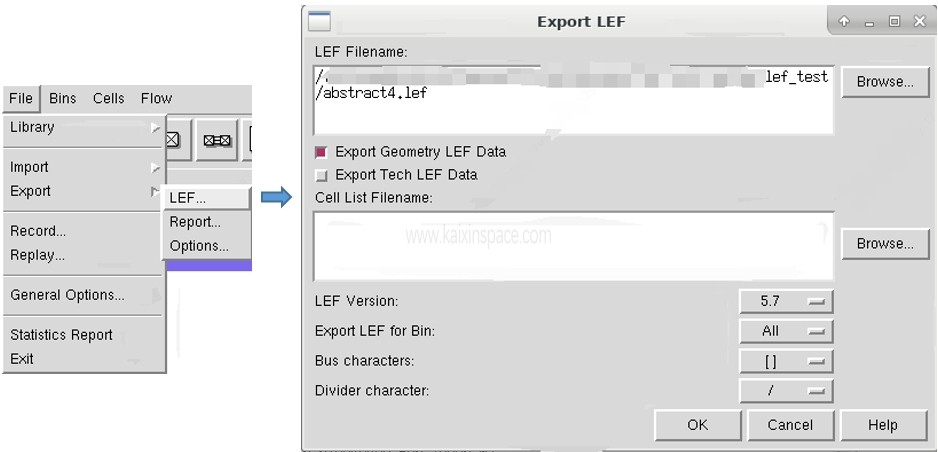

至此Abstract抽取LEF文件的步骤全部完成,最后按下图步骤导出生成的LEF文件即可。

5. 问题与讨论

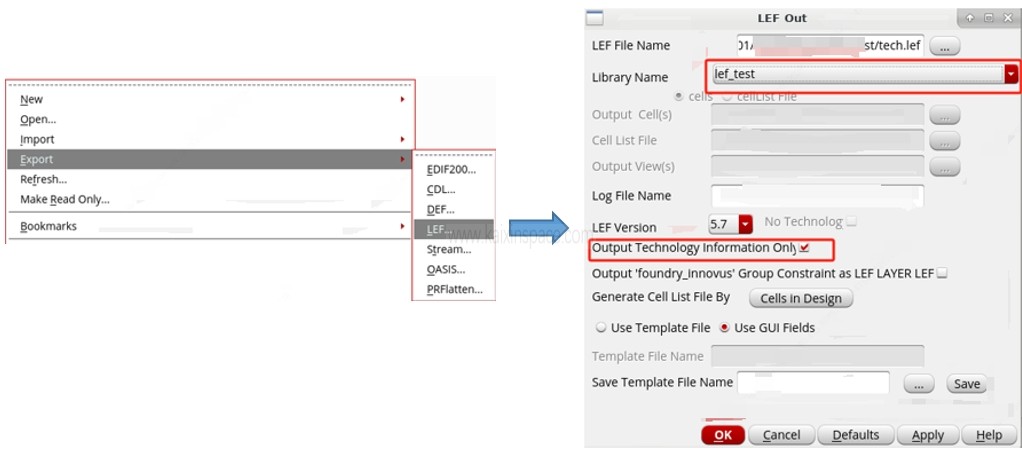

5.1 如何从techfile中提取tech.lef文件?

Ans:如下方法请参考;建议从fab获取tech.lef。

5.2 抽取LEF文件时,天线效应是必须的吗?

Ans:强烈建议抽取天线效应,因为它使得在后期的PR中,能够自动修复与优化相关长走线,避免出现Antenna错误,同时具有提高芯片可靠性和制造良率等优点。特别在当下先进工艺中,栅氧更薄,天线效应更加显著。

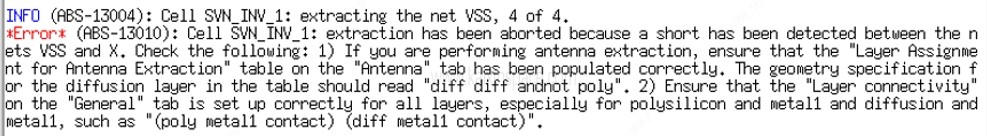

5.3 执行完Extract Step 出现错误信息时,如何解决?

Error1:

Ans:请检查”Layer Assignment for Signal Extractio“、”Layer Assignment for Power Extraction“、”Layer Assignment for Antenna Extraction“中的层是否有按上述文章中正确设定,特别要注意有源区OD的语句设定。否则可能出现error信息。

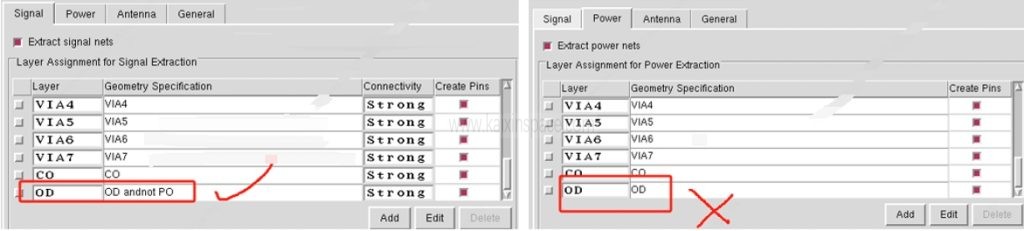

或者尝试将”Layer Assignment for Power Extraction“中的过孔层取消生成Create Pins。

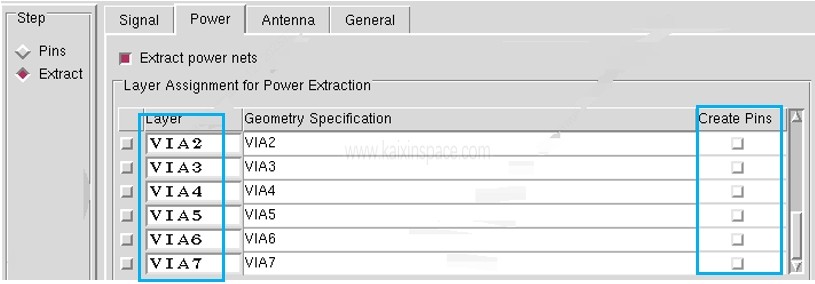

Error2:

Ans:请在Abstract软件命令行中输入相关语句即可。

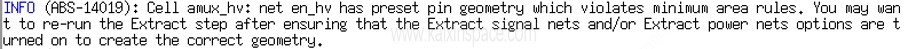

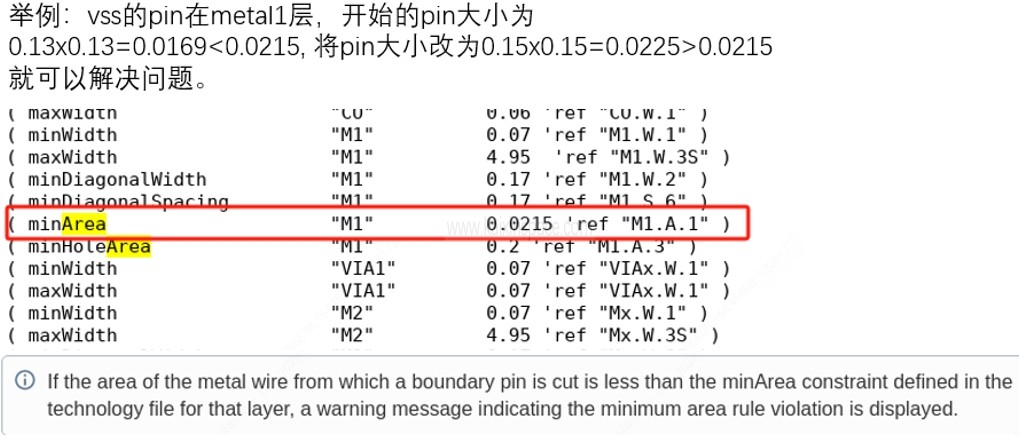

absSetOption("ExtractShapeLimit" "1000000000")5.4 执行完Abstract Step 出现警告信息,如何解决?

Ans:这是因为abstract抽取pin的最终面积尺寸小于techfile里定义的最小面积尺寸,请将pin的面积调大即可解决。

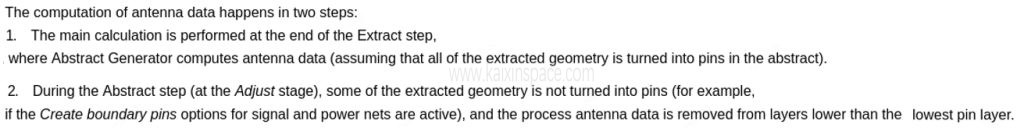

5.5 相同的pin在抽取Antenna数据时,为什么会出现不同的Antenna数据?☆

Ans:那是因为设置不同才会出现不同的Antenna数据,请参考下图。

help里有这么一段话:

欲想更进一步了解ANTENNA相关语句的具体计算方法,请参考文档《LEF/DEF 5.8 Language Reference》中的附录C:Calculating and Fixing Process AntennaViolations小节。

5.6 Abstract软件Bin栏中的”Core”、 “IO” 、”Corner”和”Block”都有什么区别?

Ans:在Abstract软件中,”Core”、 “IO” 、”Corner”和 “Block”分别代表不同类型模块的IP,它们管理着抽取视图的类型,每个类型在后端PR时,会有对应不同的设计需求和结构。换句话说,不同类型模型的IP,在抽取LEF文件时,它们里面的内容是有区别的,比如:core 类型的抽取,关注内部逻辑和性能,所以它们会保留部分信号路径;而当抽取Block类型时,我们只关注它模块边界的接口,所以我们抽取它外部的pin,而内部怎样则不需要关心。其他类型以此类推。在LEF文件中,它们以”CLASS”关键字,作为类型区分。

5.7 Abstract如何将版图中(任意位置和任意层次)没有Label相连的地方提取成pin?☆

Ans:如正文中1.4小结处所写的两种生成pin 的原则,请手动将加上相关的信息即可。

请注意:在使用方法2打开相关库并提取相关pin时,别忘记在”Map text labels to pins“栏填写对应的有效语句;

Example:任意指定版图中NW层中的部分位置为pin;

– 当你使用方法1打开相关库时,请在你想要的位置和对应的层加上对应的terminal(Label和Pin)即可,如下图:

– 当你使用方法2打开对应的库时,请在想要的地方加上对应的Label和画上想要大小的pin(相关层的propose层可以自己指定),最后你需要在Pin Step中的”Map text labels to pins“栏中指定有效生成pin的语句即可。如下图;

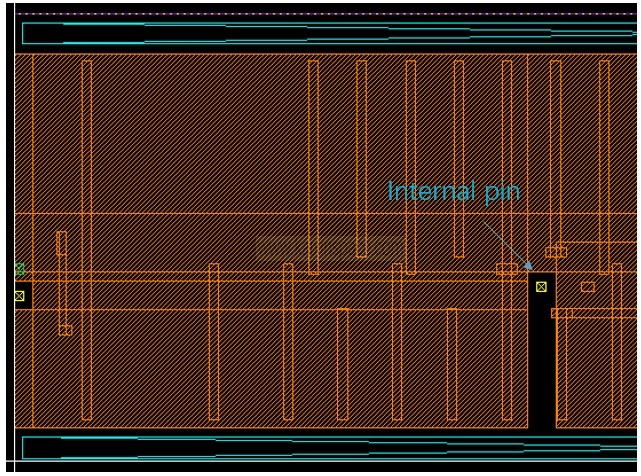

5.8 在4.2小节中,blockage选项中已经勾选了Corridor此选项,但内部的pin为什么没有生成相关边界通道?

Ans:那是因为此pin的周围被实际版图中的走线阻挡了,无法生成边界通道。要知道只有非走线的地方才会生成blockage。

5.9 抽取较大版图的LEF文件时,Abstract抽取模型花费时间太长,有什么设置可以有效减少软件提取的时间?

Ans:请参考如下几点:

(1)在Extract Step的Power Tap选项”Layer Assignment for Power Extraction“中,不勾选“Create Pins”选项;

(2)视提取lef的需要,在Abstract Step中的Adjust选项卡中,勾选”Create boundary pins”和”Create boundary pins”也可减少提取时间。

(3)按照上述文章方法2原理,在版图中提前在对应需要抽取power net上增加对应pin name,这样可以在Extract Step中省去”Extract power nets“。

5.10 使用Abstract软件抽取LEF文件和Cadence Virtuoso在CIW窗口自带的File—Export—LEF导出的方法有什么区别?

Ans:当然有区别,从设置的复杂度就能猜到,Abstract软件抽取的LEF文件内容更加丰富,但从CIW中导出的LEF文件内容比较单一仅包括Pin信息和prBoundary信息。像Antenna data、blockage data、Class、Site等信息只有Abstract才能抽取。

6. 参考

*以上内容仅供个人学习,切勿用于商业!!!