目录

1. LOCOS介绍

1.1 LOCOS定义

1.2 LOCOS技术中的”鸟嘴效应”

1.3 LOCOS技术中的”Kooi效应”,俗称:白带响应(White Ribben Effect)

2. STI技术介绍

2.1 STI定义

2.2 STI对器件的影响

3. 问题与讨论

4. 参考

1. LOCOS介绍

1.1 LOCOS全称(Local Oxidation of Silicon,局部氧化硅);是一种早期使用的隔离技术,它通过在硅衬底表面局部氧化,生成厚的二氧化硅层来隔离器件。此技术的优点是相对简单,但缺点是会产生“鸟嘴效应”(鸟嘴状的氧化硅侵入有源区)和Kooi效应(白带效应),导致占用较大的面积,因此在深亚微米工艺中被逐渐淘汰。

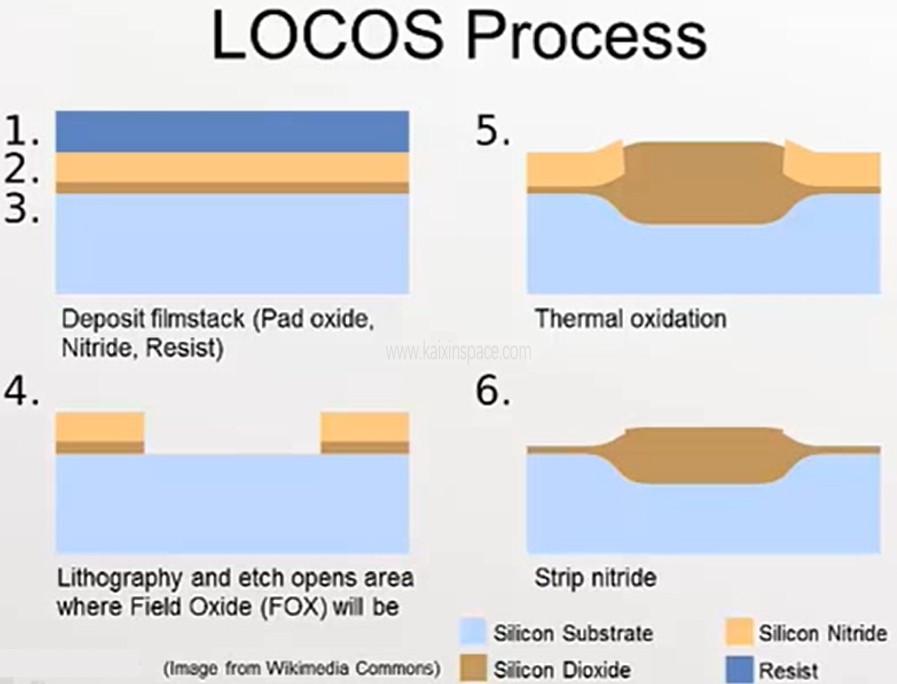

首先简单介绍下LOCOS工艺流程:

第一步:生长前置氧化层(PAD Oxide),目的是为后续生成Si3N4层缓冲对衬底的应力(3);

第二步:生长Si3N4层(它是场区氧化的阻挡层),并涂抹光刻胶(1、2);

第三步:有源区(ActiveArea)光刻和刻蚀处理(4);

第四步:场区氧化,形成硅局部场氧化物隔离器件(5);

第五步:刻蚀去除Si3N4层(6)。

1.2 LOCOS技术中的”鸟嘴效应”

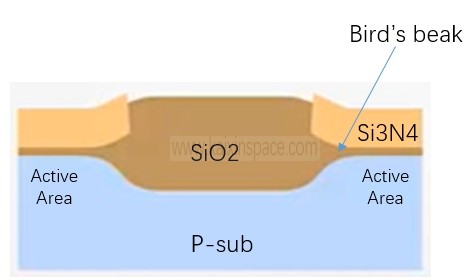

产生的原因:在 LOCOS 工艺中,氮化硅(Si₃N₄)掩膜层被用来保护有源区,而暴露的硅区域会被氧化成二氧化硅(SiO₂)。氧气或水蒸气在氧化过程中扩散到氮化硅掩膜层的边缘,并穿透到掩膜的下方,导致氧化物在掩膜边缘的硅区内扩展。这个扩展形成了类似“鸟嘴”的结构,因此称为鸟嘴效应。

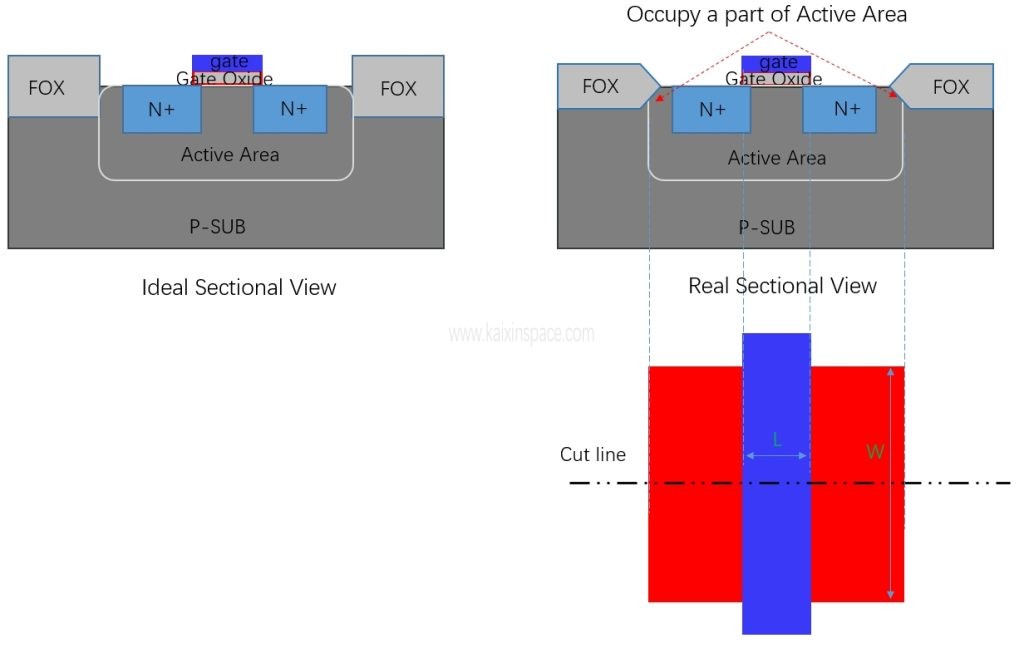

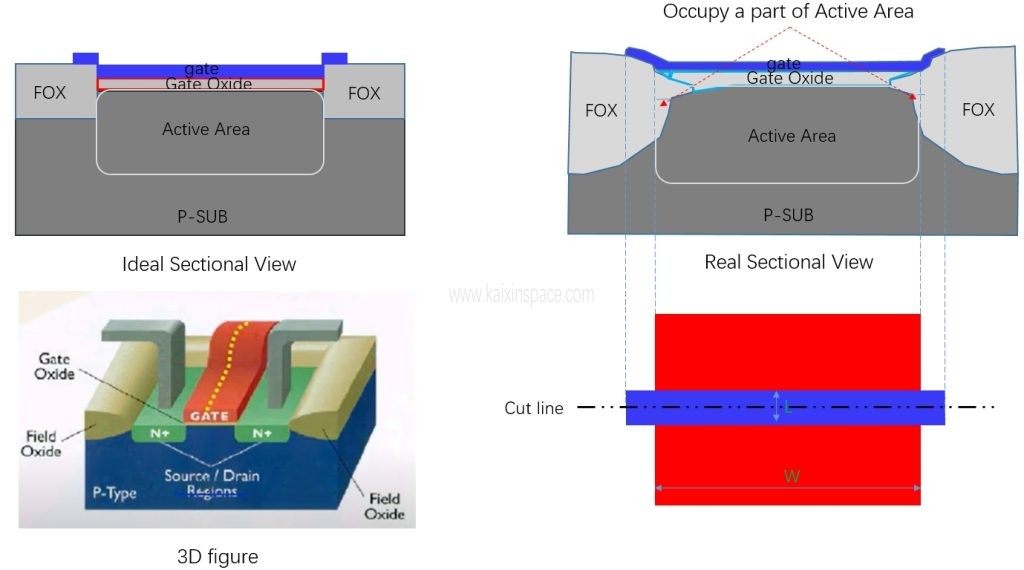

让我们从不同角度看”bird’s beak”,以下图分别是对mos管L方向和W方向切割后的截面图,

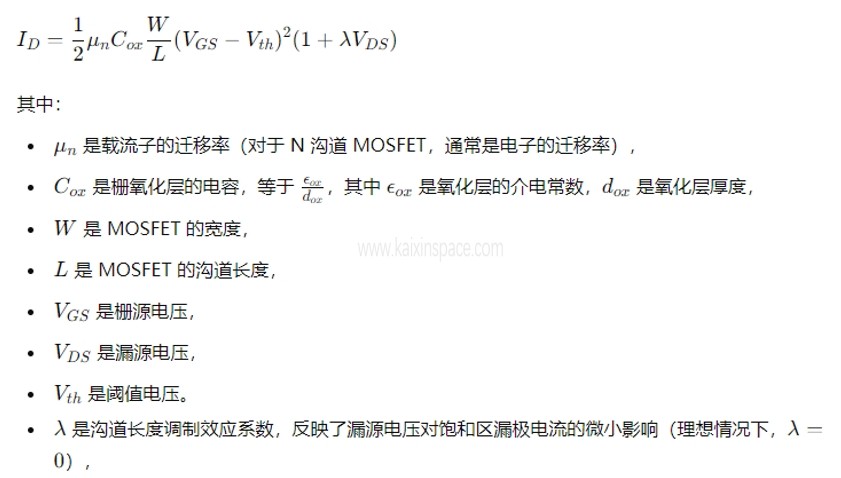

可以很明显看到在mos管有源区的四周,都有形成”鸟嘴效应”,并且侵占了有源区,这样会导致器件的有效宽度W减小,从而减小了器件的速度;器件宽度越窄,对器件本身的影响就越大。

另外从W方向的截面图可以看出,”鸟嘴效应”也同时影响了gate oxide的厚度,由于两端鸟嘴处厚度变厚,所以gate oxide 的厚度(dox)是变厚的,从而减小了Cox的容值,从而减小了器件的速度。

MOS管在饱和区的电流公式如下:

1.3 LOCOS技术中的”Kooi效应”(俗称:白带效应(White Ribben Effect))

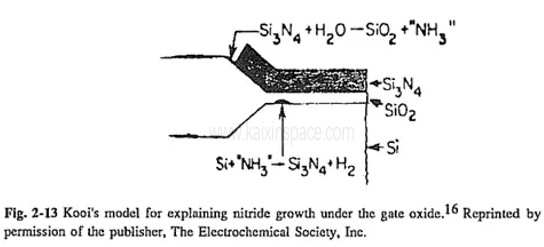

Kooi效应是由于加速LOCOS氧化的水蒸气也会撞击氮化物膜的表面产生氨。部分氨在氮化物窗口边缘附近的衬垫氧化物下面移动在那里与下层的硅反应再次生成氮化硅,这些氮化硅在有源区的边缘形成一条白带区域,并会影响后续生长的栅氧化层的质量并导致栅氧的击穿电压下降,这种效应称为白带效应。

2. STI技术介绍

2.1 STI(Shallow Trench Isolation,浅沟槽隔离) 是现代集成电路制造中常用的一种隔离技术,主要用于在深亚微米工艺(如 65nm、45nm、28nm 等)中有效隔离 MOSFET 等器件。STI 技术在芯片制造中逐渐取代了 LOCOS(局部氧化硅)隔离技术,因为它在高密度集成电路中表现出更好的性能,并能够有效解决 LOCOS 中的鸟嘴效应等问题。

首先简单介绍下STI工艺流程:

第一步:生长前置氧化层(PAD Oxide)和Si3N4层并涂抹光刻胶,(PAD Oxide)层目的是为后续生成Si3N4层缓冲对衬底的应力;

第二步:槽蚀刻;

第三步:去除光刻胶;

第四步:槽热氧化,生成SiO2,(Trench Liner oxide);

第五步:淀积多晶硅;

第六步:CMP(Chemical Mechanical Polishing),化学机械抛光,平坦化;

第七步:刻蚀去除Si3N4层。

2.2 STI对器件的一些影响

请参考本站文章:”先进工艺中几种二级效应解释”中的第3小节。

3. 问题与讨论

问题1: 在STI的制造流程中,为什么第4步和第5步要分开填充呢?为什么不合并做一步填充完整呢?

Ans:首先第4步是热氧生成SiO2(thermal SiO2),温度在1000C—1200C,生成的氧化物品质好,隔离强度高;而第5步是淀积生成SiO2,温度在700C—800C,生成氧化物品质稍差。两个步骤中工艺不一样,所以不能合并。

4. 参考

【1】The Art of Analog Layout ,Second Edition——Alan Hastings

【2】https://www.youtube.com/watch?v=jAT9eNgt4OA&list=PLGEMCz0M6AJ5DquRqU-fkGZ3dzFzQaZmP&index=3

【3】https://www.youtube.com/watch?v=qRHfUtAOOuA

【4】CMOS 集成电路闩锁效应——温德通著

【5】http://www.360doc.com/content/20/0220/16/68538116_893433570.shtml