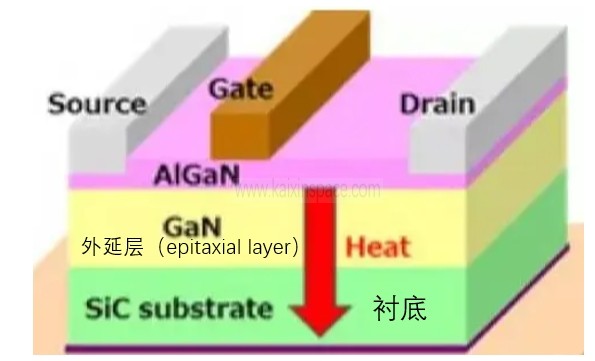

1. 外延层定义:

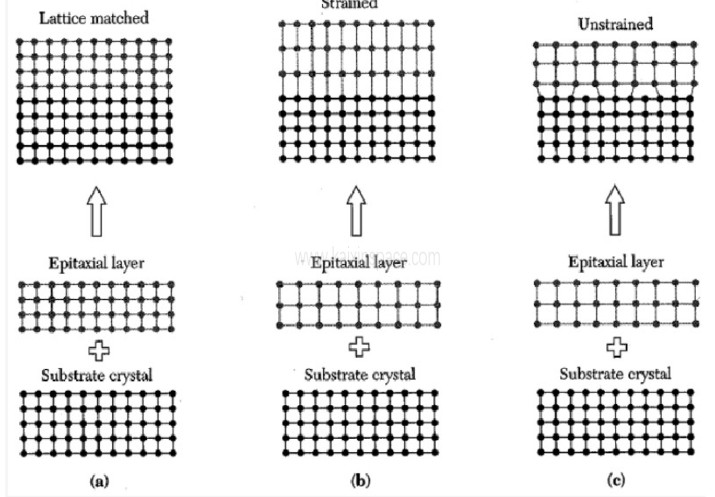

是指在单晶衬底(基片)上沉积一层具有特定晶体取向和化学成分的薄膜;犹如原来的晶体向外延伸了一段。新单晶可以与衬底为同一材料,也可以是不同材料(同质外延或者是异质外延)。由于新生单晶层按衬底晶相延伸生长,从而被称之为外延层(厚度通常为几微米),而长了外延层的衬底称为外延片,器件制作在外延层上为正外延,若器件制作在衬底上则称为反外延,此时外延层只起支撑作用。

外延层:衬底上新生长的单晶层;

外延片:生长了外延层的衬底,即:外延片=外延层+衬底;

2. 使用外延层的好处

2.1 提高PN结的击穿电压

击穿电压(Breakdown Voltage)是一个关键指标,决定了器件在高压条件下的稳定性。

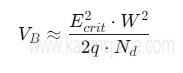

相关近似公式:

其中:Ecrit:硅的临界电场;

W:漂移区宽度;

Nd:衬底(外延层)掺杂浓度;

q:电荷量

从公式可以明显看出,击穿电压VB反比于外延层掺杂浓度Nd,当外延层掺杂浓度降低时,击穿电压增大。通过控制外延层的掺杂浓度,可以精确设计器件的击穿电压。

2.2 掺杂控制与阈值电压调节

阈值电压(Threshold Voltage, VTH)是MOSFET中控制开关行为的关键参数。通过外延层中的精确掺杂,可以优化VTH.

相关近似公式:

从公式可以明显看出,VTH正比于外延层掺杂浓度NA。

如果外延层的掺杂浓度较高,则VTH 增加,使得器件更难导通;通过降低外延层的掺杂浓度,可以降低阈值电压,使器件更容易导通。

2.3 减小寄生电容和寄生电阻

寄生效应会降低器件的开关速度和频率响应。外延层通过提供高阻区,可以减少寄生电容;而通过增加衬底掺杂浓度来降低电阻率,从而减小寄生电阻。

以上只是介绍了外延层几个优点,然而外延层还有很多优点比如:优化电子迁移率、好的热导率和散热性能等等。

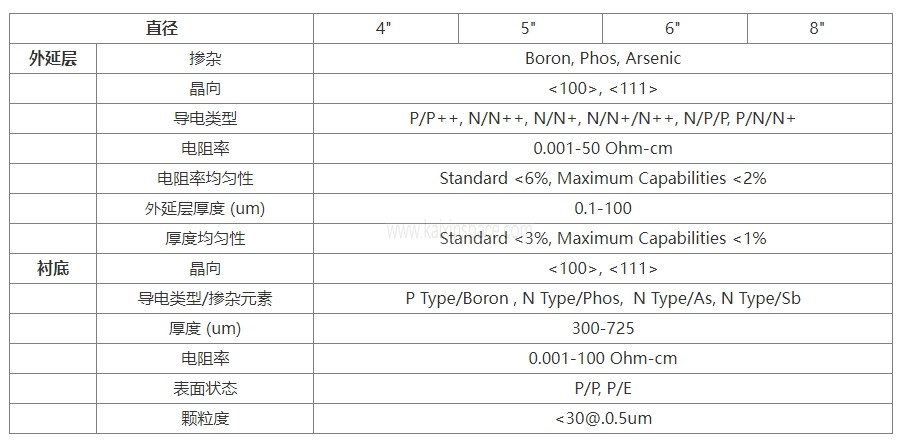

3. 外延层常见的工艺参数

4. 问题与讨论

问题1. 衬底和外延层使用的是单晶硅还是多晶硅呢?

Ans:衬底和外延层通常使用的是单晶硅,而不是多晶硅;因为单晶硅具有均匀的晶体结构,单晶硅的原子排列非常有序,几乎没有晶界缺陷。另外单晶硅也具有较高的载流子迁移率和较低的电阻率。而多晶硅经常用于制造MOSFET的栅极或互连层,因为它可以通过掺杂调整电阻率,并且具有良好的热稳定性。

问题2. 为什么外延层低掺杂p-,不会和下面的衬底高掺杂p+发生浓度扩散呢?

Ans:掺杂浓度差确实会导致一些扩散现象,但通过合理的设计和工艺控制,这种扩散可以被有效抑制,保证外延层的特性。以下是列举的其中几个相关措施:

- 外延生长的低温工艺;

- 外延层生长时间的控制;

- 掺杂浓度梯度设计;

- 衬底和外延层之间的界面质量的控制;

问题3. 为什么外延层可以降低闩锁效应?

Ans:请参考本站文章:一文搞懂闩锁效应的第3.1.4小节。

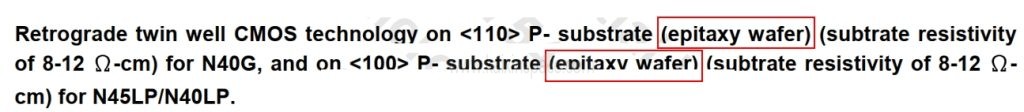

问题4. 如何确定自己使用的工艺是否有用外延层?

Ans:一般情况下在design rule 前几页,有Technology Overview一节中会有介绍。

参考:

【1】http://www.iawbs.com/portal.php?mod=view&aid=1432

【2】https://www.plutosemi.com/show-104-423-1.html