本文通过对电容不同过孔扇出方式的仿真分析,来找到哪一种fanout最优;并分析不同的过孔fanout之间它们会造成的阻抗差异有多大。最后给出几种过孔fanout设计的优先级,以给PDN中layout设计作为参考。

—-这里我们用案例仿真来观察相关的阻抗变化。

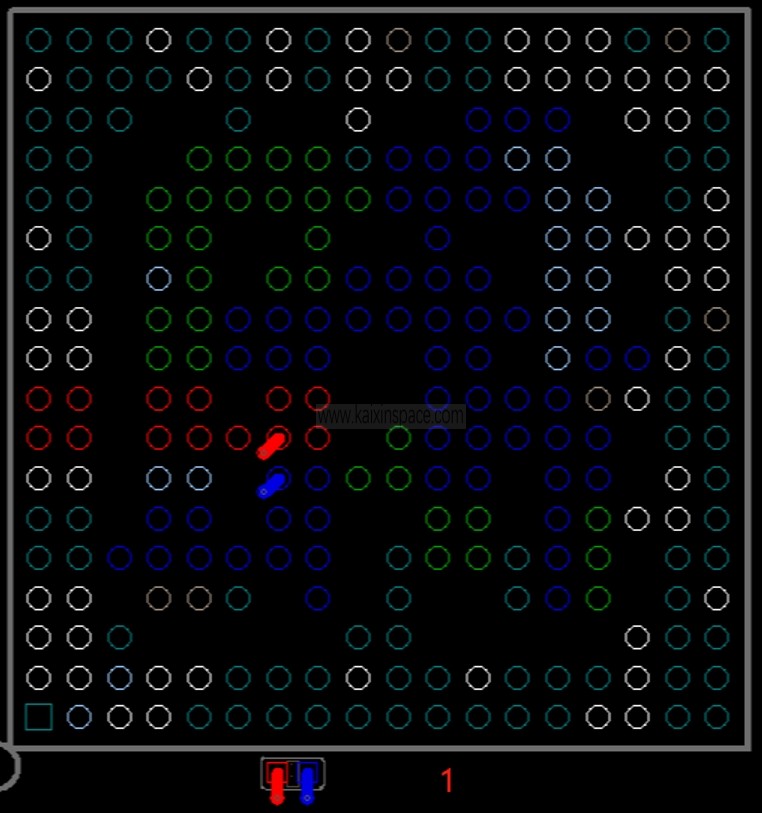

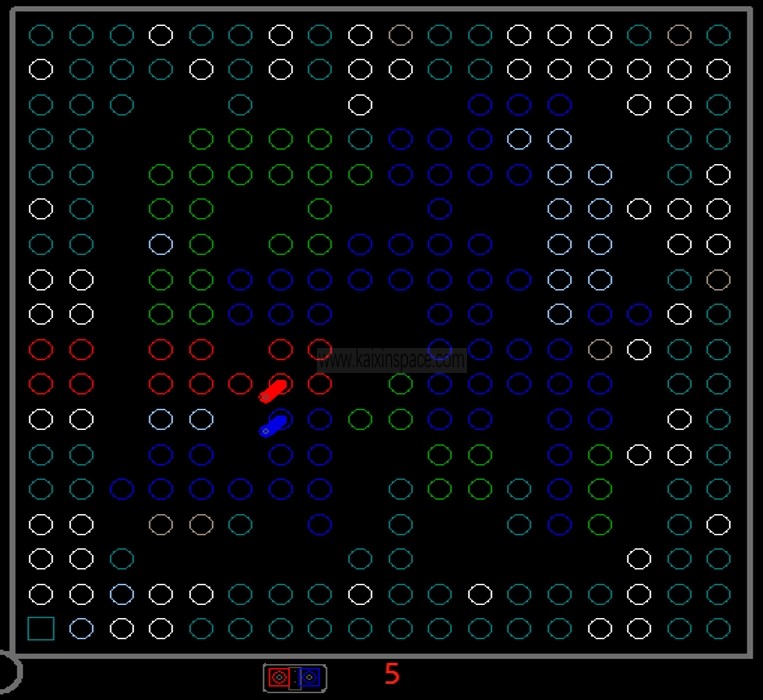

设计一个包含一颗IC和一颗电容的pcb,如下图所示。

实验板相关参数:

- 尺寸大小:16.8×15.5mm

- 叠构:Top—Gnd02—Pwr03—Bottom

- 介电常数和损耗正切值分别为:4.5和0.02

- 铜厚:1oz

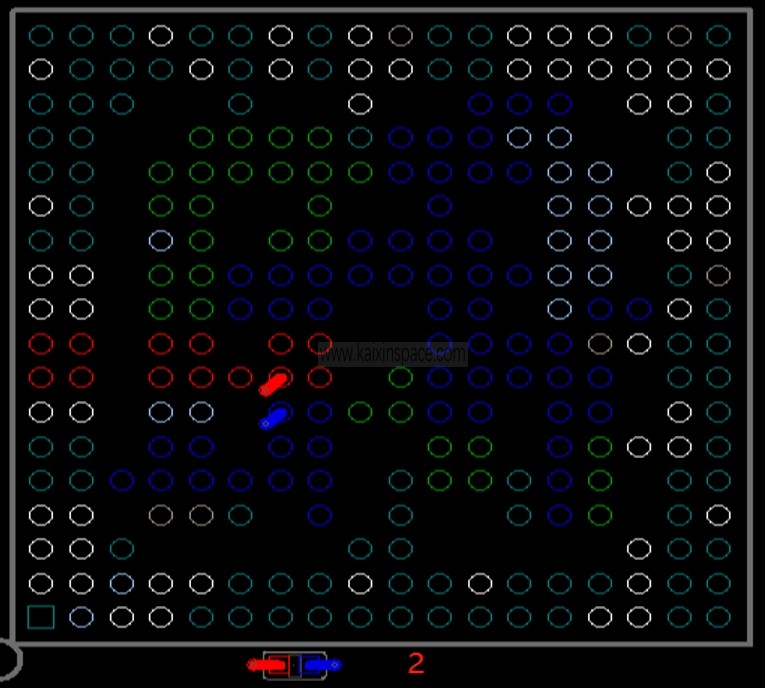

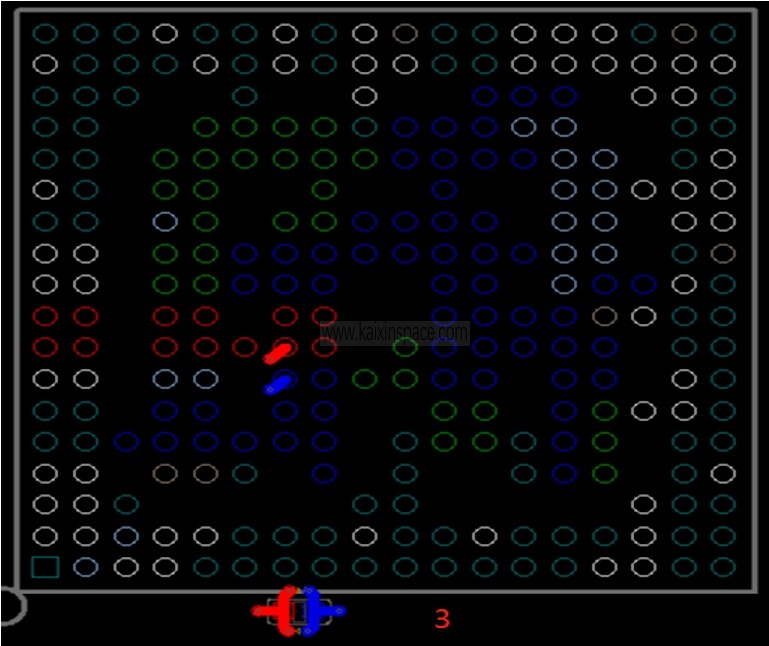

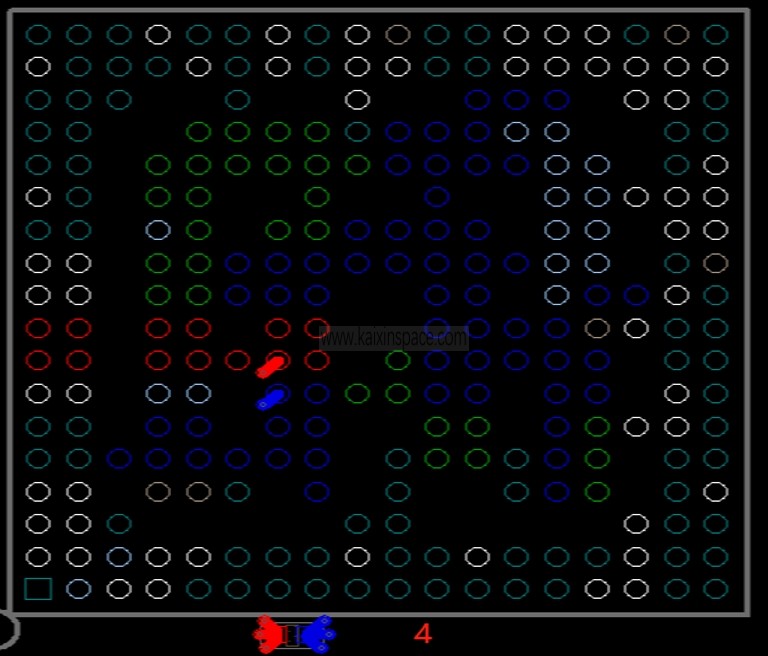

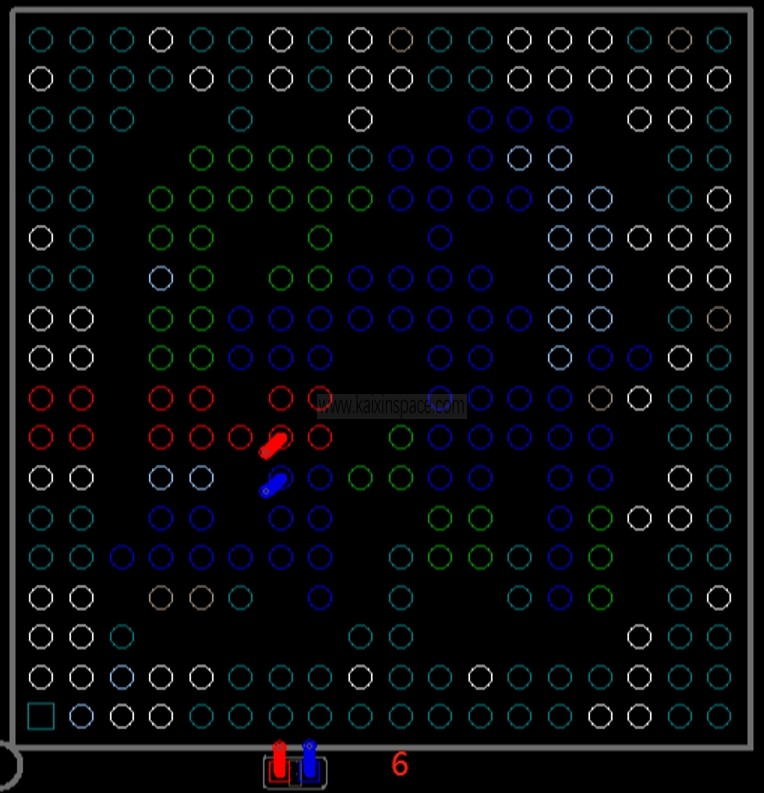

电容不同过孔fanout的6种方式,如下图所示:红色net代表power,蓝色net代表gnd。

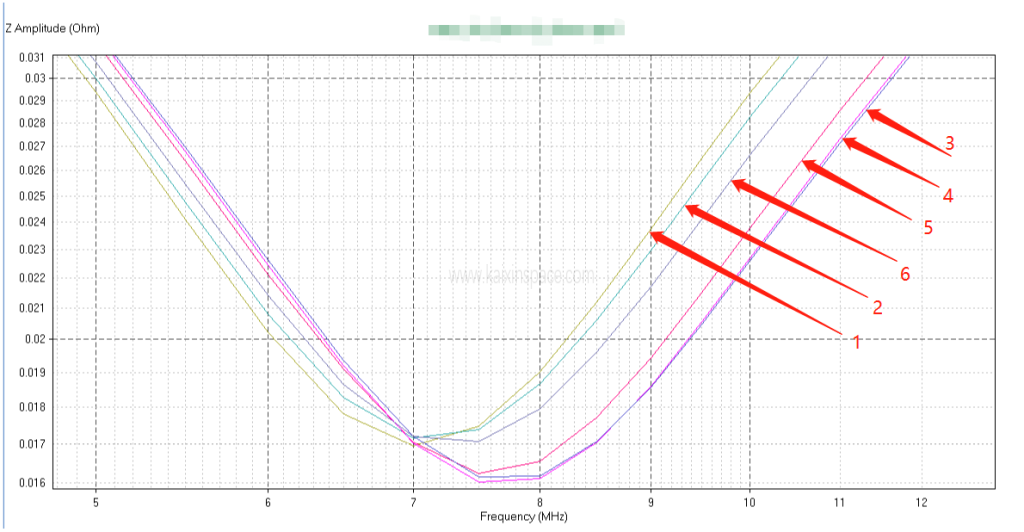

电容不同过孔fanout方式,对应仿真的得到的z阻抗曲线如下图:

从上面阻抗曲线可以看出:

- 在谐振点右边,电容过孔fanout方式3,阻抗最小,这是因为pwr和gnd网络过孔相互靠近,形成互感抵消现象,另外相同过孔并联也有效减小电感;

- 可以看到阻抗值fanout方式4仅次于fanou3,这是因为fanout4仅有相同过孔并联减小电感,没有互感抵消;

- 另外也可以看出,随着电容安装电感的增大,谐振点左移,去耦效果变差。

总结:

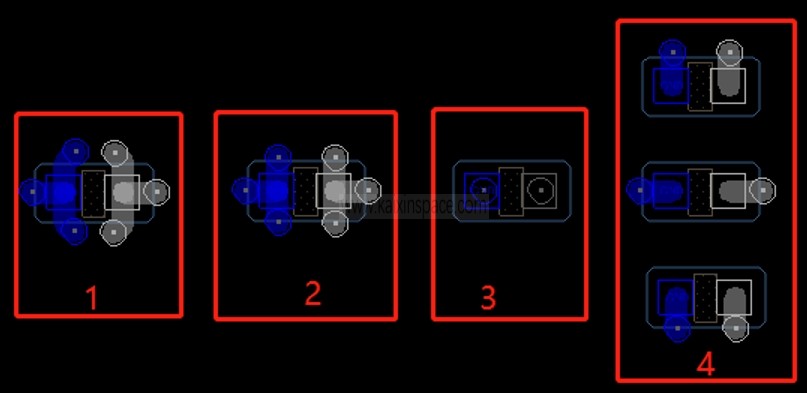

(1)实际项目设计中电容Fanout方式(列出常见几种)优先级如下:

说明:“1”优先级最高,“4”优先级最低;

(2)电容过孔fanout:不相同电流Via尽量靠近,相同电流Via间距加大(一般Via水平间距大于Via长度距离即可)。

-END-